République Algérienne Démocratique et Populaire

Ministère de l'Enseignement Supérieur

Et de la Recherche Scientifique

Ecole Supérieure en Sciences

Appliquées D'Alger (ESSAA)

DEPARTEMENT DE SECOND CYCLE – GENIE ELECTRIQUE

OPTION : TRACTION ELECTRIQUE

**POLYCOPIE PEDAGOGIQUE**

Pour l'obtention de

**L'HABILITATION UNIVERSITAIRE**

Spécialité : Electronique

Rédigé par

**Dr. Mahmoud ARBID**

Intitulé

**COURS DE SYSTEMES

NUMERIQUES 01**

Année universitaire 2019/2020

بِسْمِ اللَّهِ الرَّحْمَنِ الرَّحِيمِ

© Copyright by Mahmoud ARBID 2019

All Rights Reserved

# Table des matières

|                                                                  | Page     |

|------------------------------------------------------------------|----------|

| <b>CHAPITRE</b>                                                  |          |

| <b>AVANT PROPOS</b>                                              | <b>1</b> |

| <b>I Logique combinatoire</b>                                    | <b>2</b> |

| <b>1. REPRÉSENTATION NUMÉRIQUE DE L'INFORMATION</b>              | <b>3</b> |

| 1.1 Représentation des nombres .....                             | 3        |

| 1.2 Systèmes de numérations .....                                | 3        |

| 1.3 Conversion d'un système de numération .....                  | 4        |

| 1.3.1 Conversion de la base B vers 10 .....                      | 4        |

| 1.3.2 Conversion de la base 10 vers B .....                      | 4        |

| 1.3.2.1 1 <sup>ère</sup> Méthode (Soustraction successive) ..... | 4        |

| 1.3.2.2 2 <sup>ème</sup> Méthode (Division) .....                | 4        |

| 1.3.3 Généralisation de la conversion en puissance de 2 .....    | 5        |

| 1.3.3.1 Conversion de la base $2^n$ vers la base n .....         | 5        |

| 1.3.3.2 Conversion de la base 2 vers la base $2^n$ .....         | 5        |

| 1.3.3.3 Conversion de la base 'i' vers la base 'j' .....         | 5        |

| 1.3.4 L'arithmétique binaire .....                               | 6        |

| 1.3.4.1 Les opérations .....                                     | 6        |

| 1.4 Codage des entiers .....                                     | 6        |

| 1.4.1 Les codes pondérés .....                                   | 7        |

| 1.4.1.1 Codage binaire pur .....                                 | 7        |

| 1.4.1.2 Codage DCB (Décimal Codé Binaire) .....                  | 7        |

| 1.4.1.3 Codage binaire signé .....                               | 7        |

| 1.4.1.4 Codage en complément à 1 (Complément restreint) .....    | 7        |

| 1.4.1.5 Codage en complément à 2 (Complément vrai) .....         | 8        |

|           |                                                                 |           |

|-----------|-----------------------------------------------------------------|-----------|

| 1.4.2     | Les codes non pondérés .....                                    | 9         |

| 1.4.2.1   | Codage excédent 3 .....                                         | 9         |

| 1.4.2.2   | Codage binaire réfléchi (GRAY) .....                            | 9         |

| 1.5       | Représentation des nombres réels .....                          | 9         |

| 1.5.1     | Virgule fixe .....                                              | 9         |

| 1.5.2     | Virgule flottante .....                                         | 10        |

| <b>2.</b> | <b>ALGÈBRE DE BOOLE ET FONCTIONS LOGIQUES .....</b>             | <b>11</b> |

| 2.1       | Définition .....                                                | 11        |

| 2.2       | Opérations et fonctions de base de l'algèbre de Boole .....     | 11        |

| 2.2.1     | Fonction à une seule variable .....                             | 11        |

| 2.2.2     | Fonction à deux variables .....                                 | 11        |

| 2.2.2.1   | Opérateur ET (AND) .....                                        | 11        |

| 2.2.2.2   | Opérateur OU (OR) .....                                         | 12        |

| 2.2.2.3   | Opérateur Non ET (NAND) .....                                   | 12        |

| 2.2.2.4   | Opérateur Non OU (NOR) .....                                    | 12        |

| 2.2.2.5   | Opérateur OU Exclusif (XOR) .....                               | 13        |

| 2.2.2.6   | Opérateur Non OU Exclusif (XNOR) .....                          | 13        |

| 2.2.2.7   | Les portes universelles .....                                   | 13        |

| 2.3       | Axiomes ou lois fondamentales de l'algèbre de Boole .....       | 14        |

| 2.4       | Relations de base dans l'algèbre de Boole .....                 | 14        |

| 2.5       | Théorèmes de MORGAN .....                                       | 15        |

| 2.6       | Représentation des fonctions booléennes .....                   | 15        |

| 2.6.1     | Mintermes / Maxtermes .....                                     | 15        |

| 2.6.2     | Formes canoniques .....                                         | 15        |

| 2.6.3     | La représentation numérique .....                               | 16        |

| 2.6.4     | Représentation par le diagramme de Karnaugh .....               | 16        |

| 2.6.5     | Simplification des fonctions booléennes .....                   | 17        |

| 2.6.6     | Les règles importantes pour lire un diagramme de Karnaugh ..... | 19        |

| 2.6.7     | Les fonctions incomplètement définies .....                     | 19        |

| 2.6.8     | Synthèse des systèmes combinatoires .....                       | 20        |

| 2.7       | Quelques circuits intégrés logiques usuels .....                | 21        |

| <b>3.</b> | <b>CIRCUITS COMBINATOIRES USUELS .....</b>                      | <b>22</b> |

| 3.1       | Objectif .....                                                  | 22        |

| 3.2       | Les circuits arithmétiques .....                                | 22        |

| 3.2.1     | L'additionneur binaire .....                                    | 22        |

| 3.2.1.1   | Le demi-additionneur ( $\frac{1}{2}$ ADD) .....                 | 22        |

| 3.2.1.2   | L'additionneur complet (ADD) .....                              | 22        |

| 3.2.2     | Le soustracteur binaire .....                                   | 24        |

| 3.2.2.1   | Le demi-soustracteur ( $\frac{1}{2}$ SOUST) .....               | 24        |

| 3.2.2.2   | Le soustracteur complet (SOUST) .....                           | 24        |

|           |                                                                            |           |

|-----------|----------------------------------------------------------------------------|-----------|

| 3.2.3     | Les comparateurs . . . . .                                                 | 26        |

| 3.3       | Les circuits de transcodage . . . . .                                      | 26        |

| 3.3.1     | Le codeur (encodeur) . . . . .                                             | 27        |

| 3.3.2     | Le décodeur . . . . .                                                      | 27        |

| 3.3.3     | Le transcodeur . . . . .                                                   | 29        |

| 3.4       | Les circuits d'aiguillage . . . . .                                        | 29        |

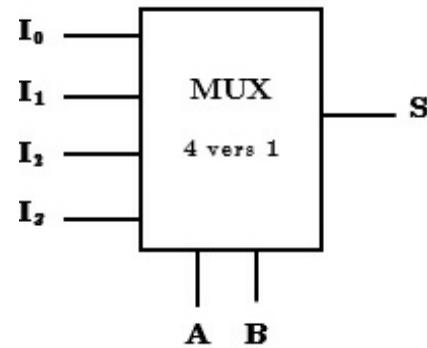

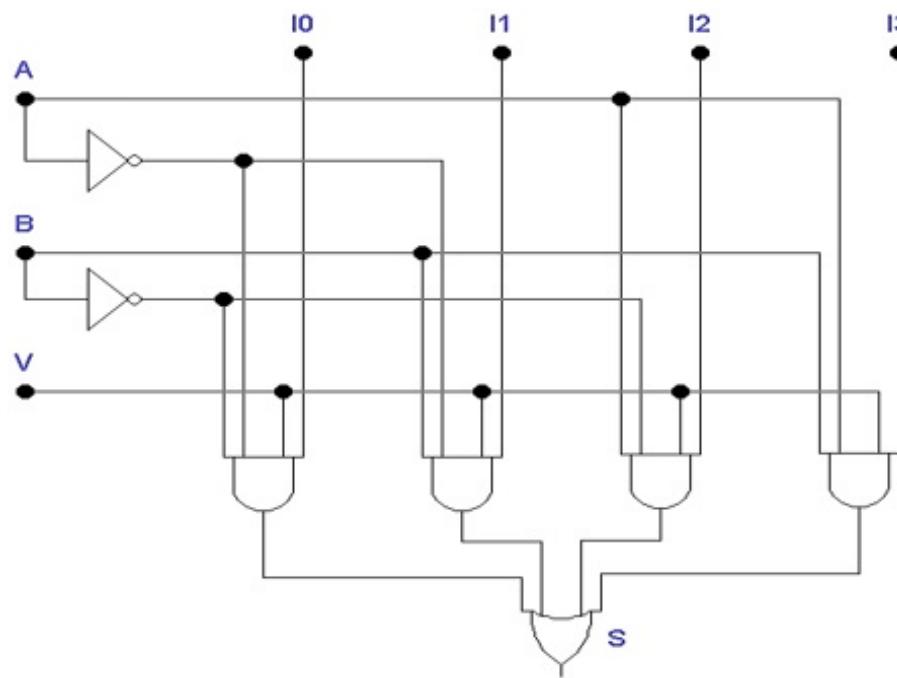

| 3.4.1     | Le multiplexeur ( <i>MUX</i> ) . . . . .                                   | 29        |

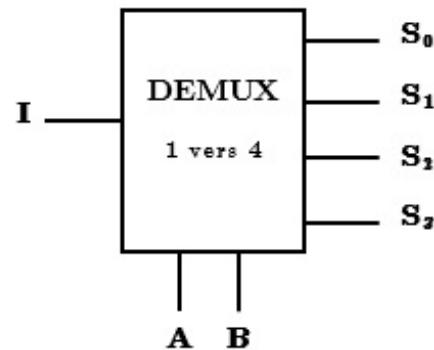

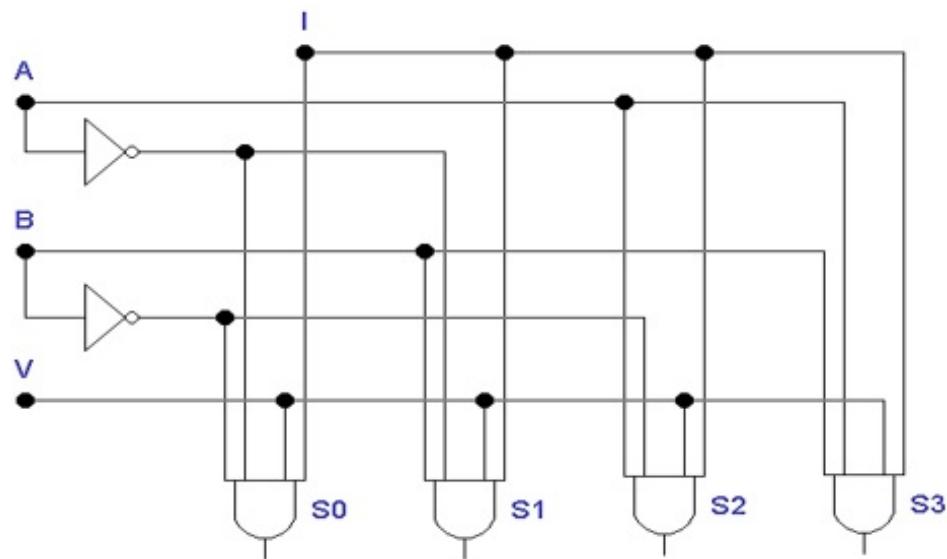

| 3.4.2     | Le démultiplexeur ( <i>DEMUX</i> ) . . . . .                               | 30        |

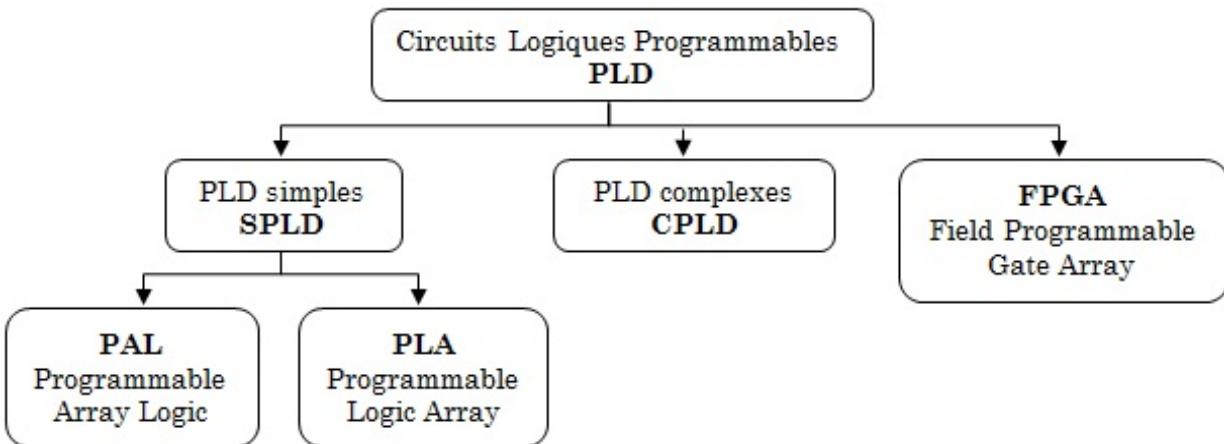

| 3.5       | Circuits logiques programmables (PLD) . . . . .                            | 31        |

| 3.5.1     | Logique fixe ou logique programmable . . . . .                             | 32        |

| 3.5.2     | Les circuits logiques programmables simples (SPLD) . . . . .               | 32        |

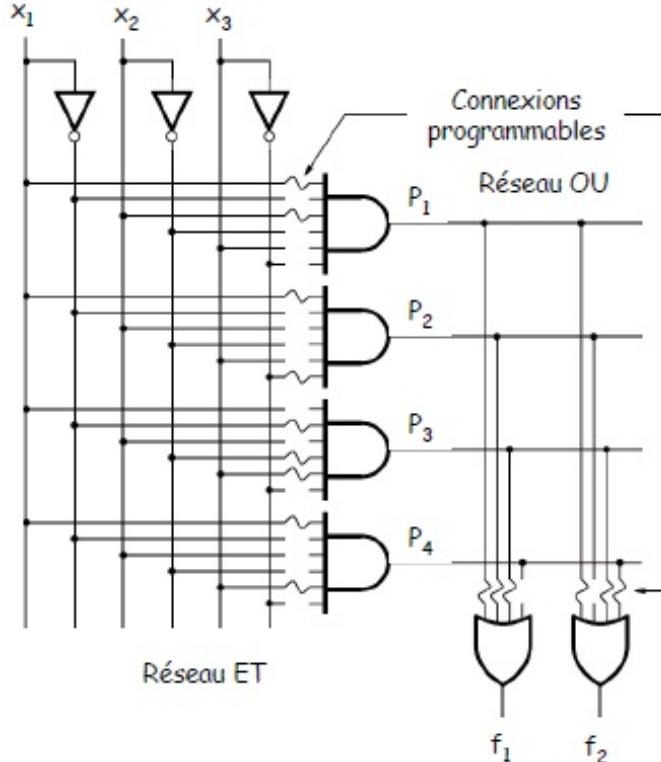

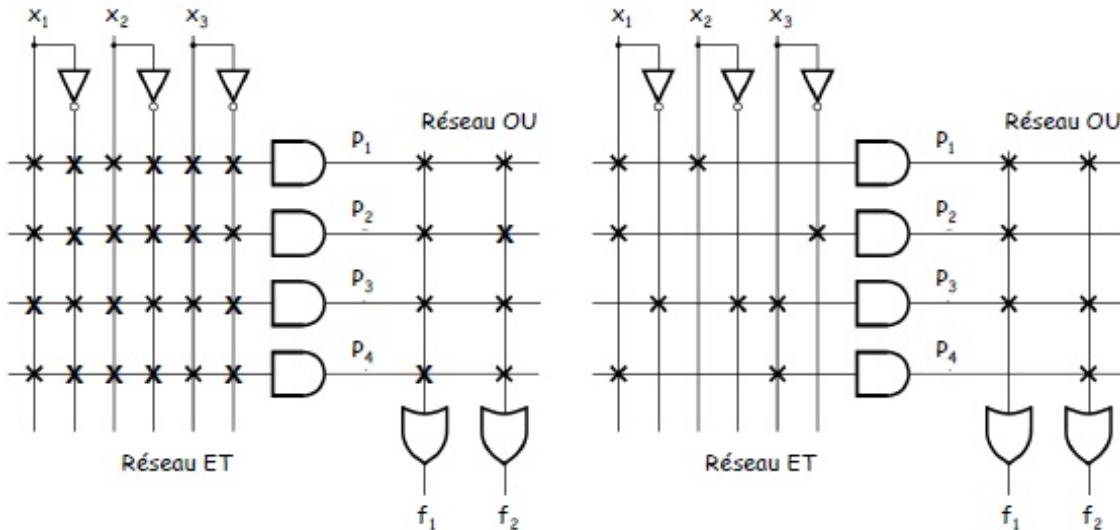

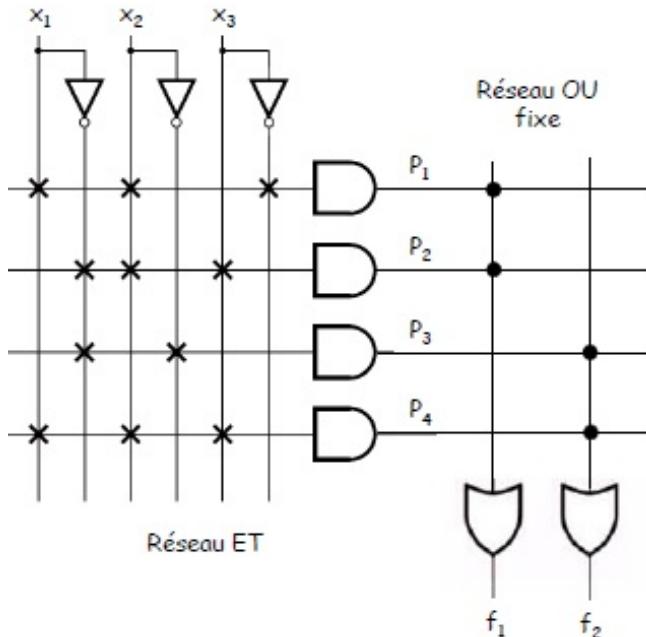

| 3.5.2.1   | Structure des SPLD . . . . .                                               | 32        |

| 3.5.2.2   | Les Programmable Logic Array (PLA) . . . . .                               | 32        |

| 3.5.2.3   | Les Programmable Array Logic (PAL) . . . . .                               | 33        |

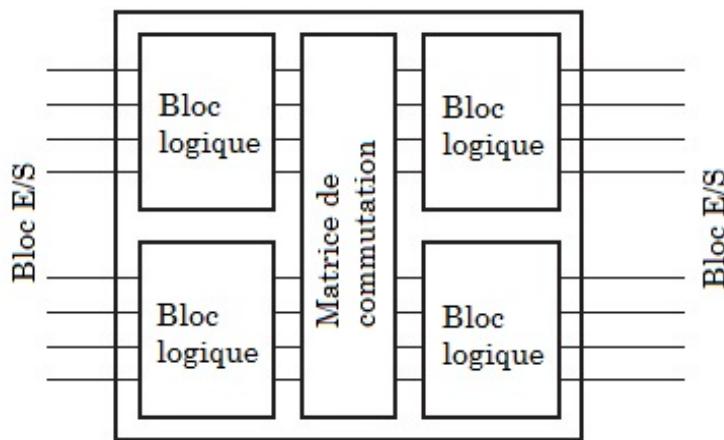

| 3.5.3     | Les Complex Programmable Logic Device (CPLD) . . . . .                     | 35        |

| <b>II</b> | <b>Logique séquentielle</b>                                                | <b>36</b> |

| <b>4.</b> | <b>INTRODUCTION AUX CIRCUITS SÉQUENTIELS</b> . . . . .                     | <b>37</b> |

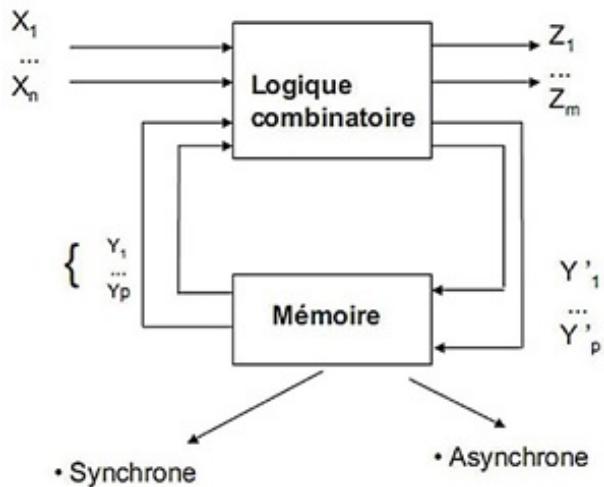

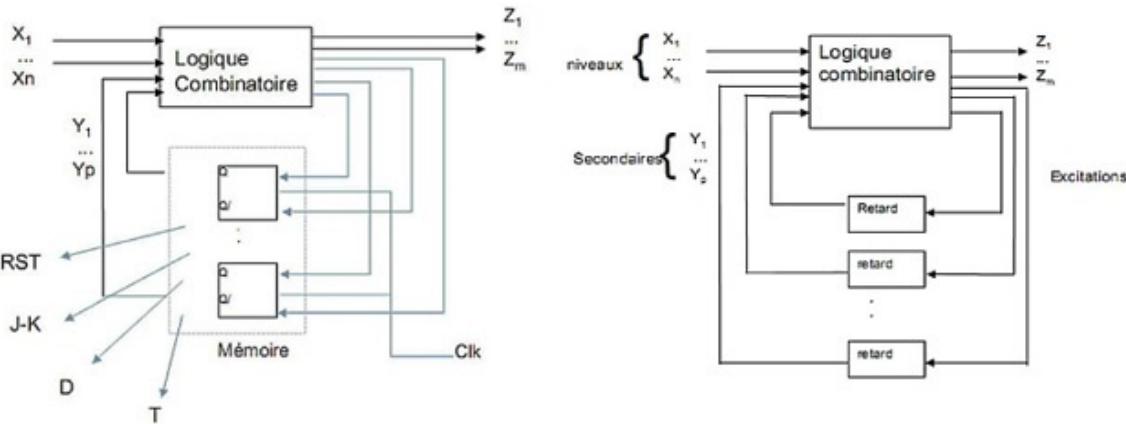

| 4.1       | Du combinatoire au séquentiel . . . . .                                    | 37        |

| 4.1.1     | Circuits séquentiels asynchrones . . . . .                                 | 37        |

| 4.1.2     | Circuits séquentiels synchrones . . . . .                                  | 37        |

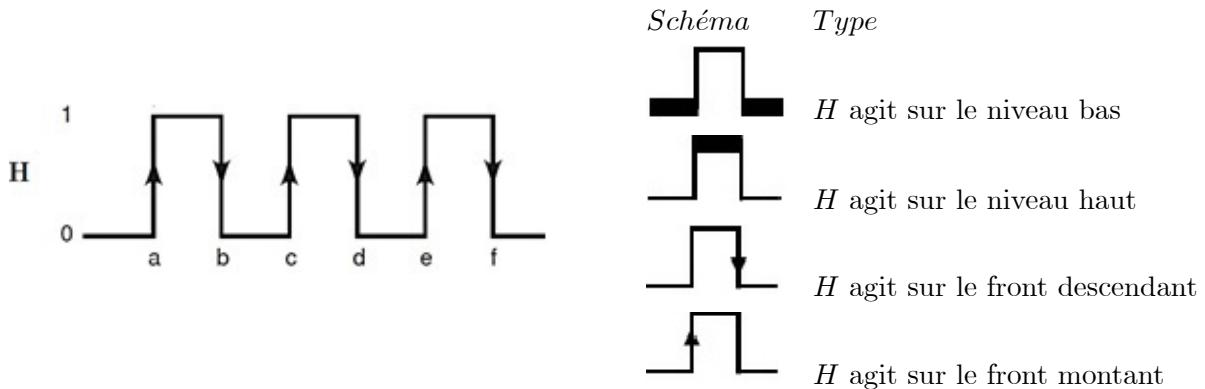

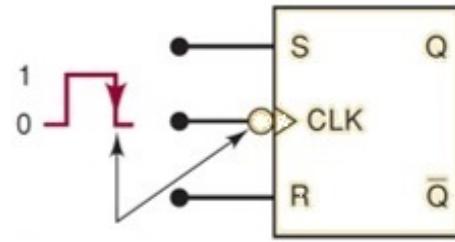

| 4.2       | L'horloge (H) ou Clock (CLK) . . . . .                                     | 38        |

| 4.3       | Les bascules . . . . .                                                     | 38        |

| 4.3.1     | Définition . . . . .                                                       | 38        |

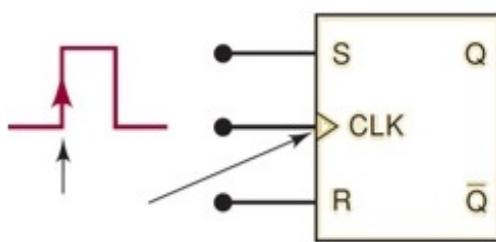

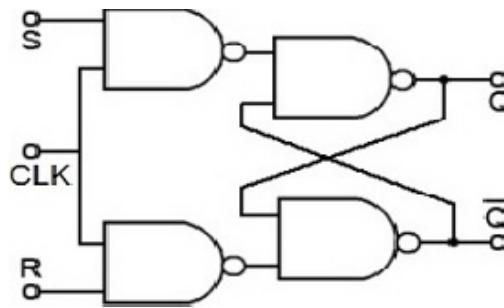

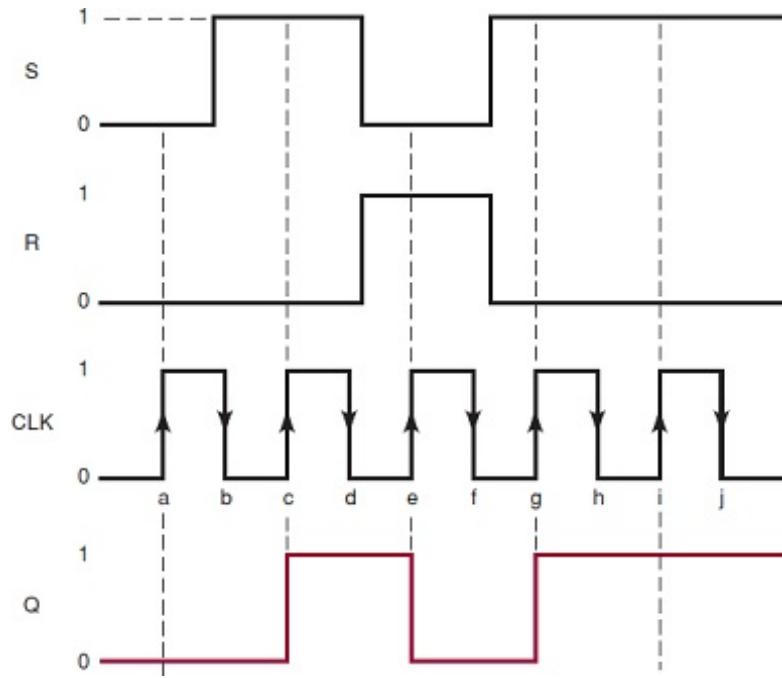

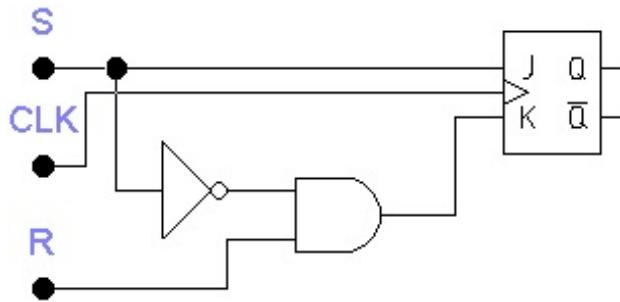

| 4.3.2     | Bascule SR . . . . .                                                       | 38        |

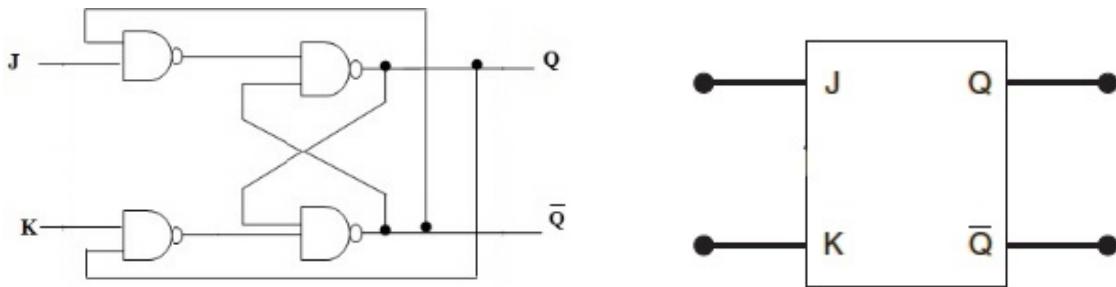

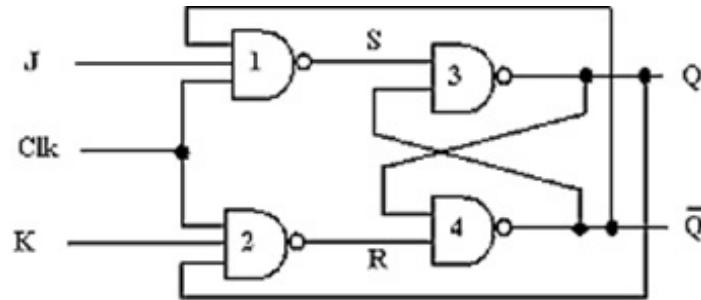

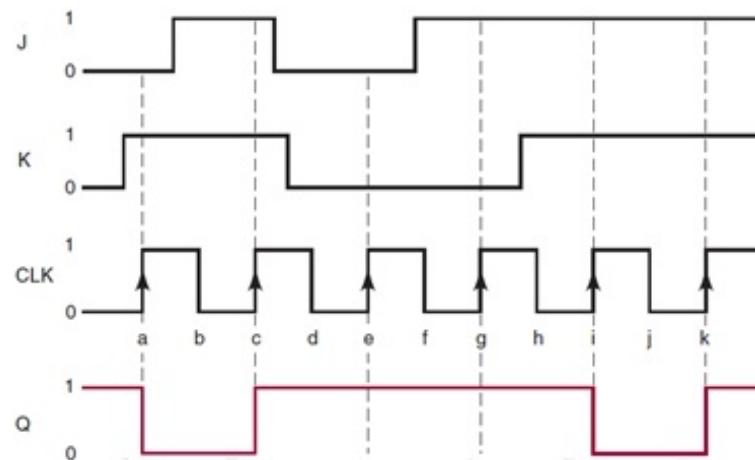

| 4.3.3     | Bascule JK . . . . .                                                       | 40        |

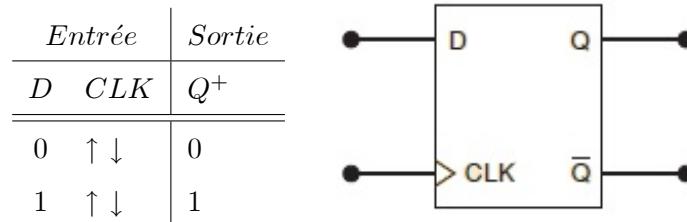

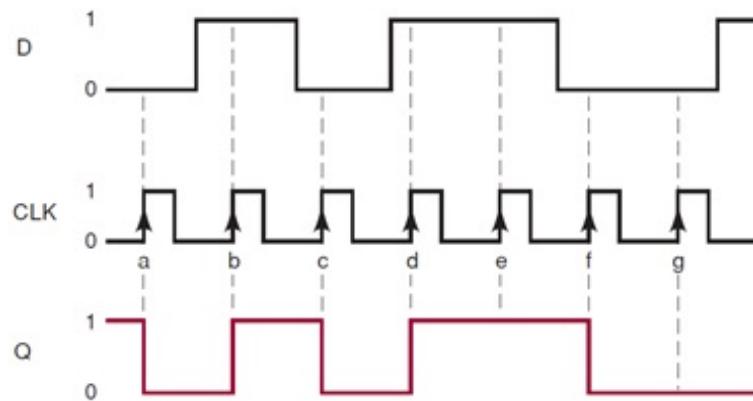

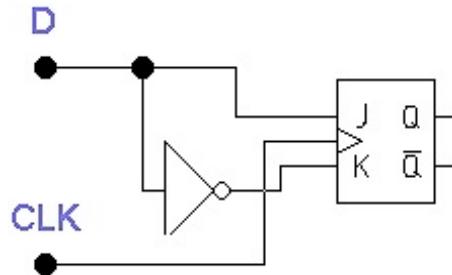

| 4.3.4     | Bascule D . . . . .                                                        | 43        |

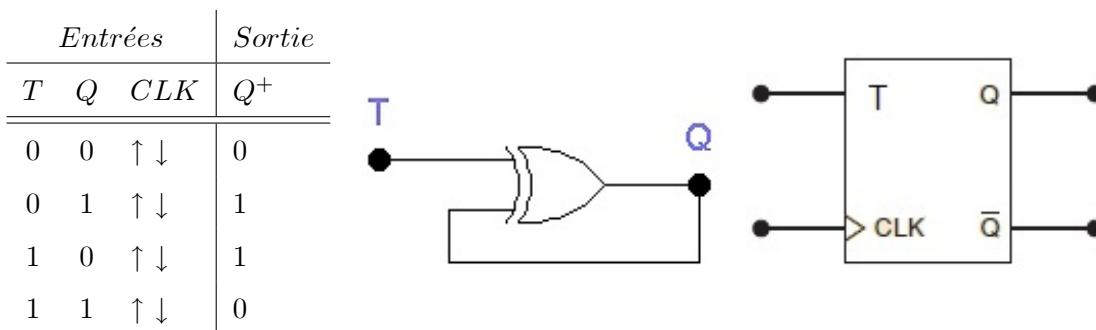

| 4.3.5     | Bascule T . . . . .                                                        | 43        |

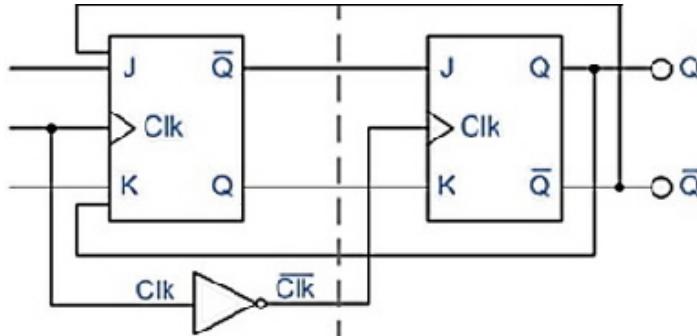

| 4.3.6     | Bascule maître-esclave . . . . .                                           | 44        |

| 4.3.7     | Réalisation des bascules synchrones SR, D et T en fonction de JK . . . . . | 44        |

| 4.3.7.1   | SR en fonction de JK . . . . .                                             | 44        |

| 4.3.7.2   | D en fonction de JK . . . . .                                              | 44        |

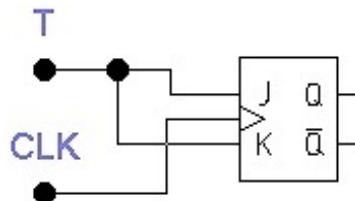

| 4.3.7.3   | T en fonction de JK . . . . .                                              | 45        |

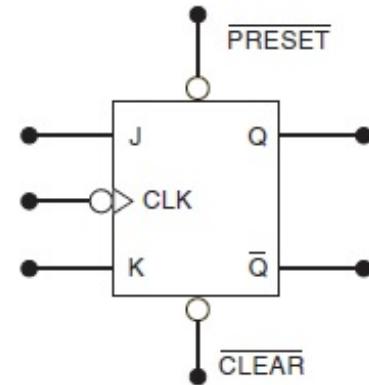

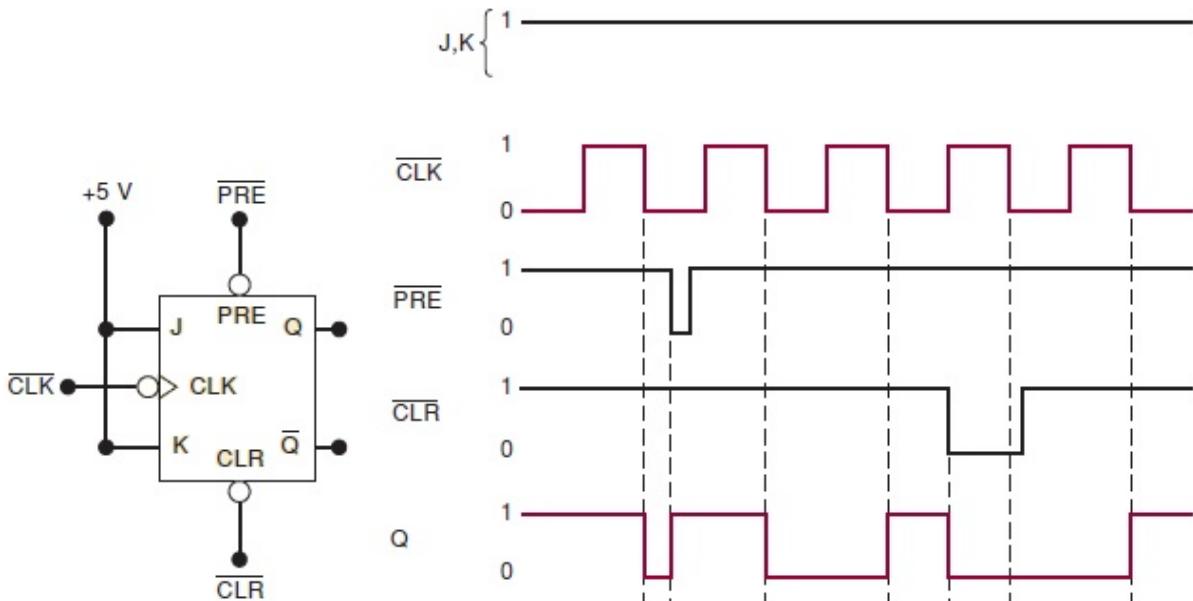

| 4.4       | Les entrées asynchrones . . . . .                                          | 45        |

| 4.5       | Les registres . . . . .                                                    | 47        |

| 4.5.1     | Définition d'un registre . . . . .                                         | 47        |

| 4.5.1.1   | La mémorisation . . . . .                                                  | 47        |

| 4.5.1.2   | Le décalage . . . . .                                                      | 47        |

| 4.5.1.3   | Le comptage (Décomptage) . . . . .                                         | 47        |

|                            |                                                     |           |

|----------------------------|-----------------------------------------------------|-----------|

| 4.5.2                      | Les type de décalage .....                          | 47        |

| 4.5.2.1                    | Décalage à gauche .....                             | 47        |

| 4.5.2.2                    | Décalage à gauche .....                             | 48        |

| 4.5.2.3                    | Décalage circulaire .....                           | 48        |

| 4.6                        | Les compteurs .....                                 | 48        |

| 4.6.1                      | Définition .....                                    | 48        |

| 4.6.2                      | Capacité de comptage .....                          | 48        |

| 4.6.3                      | Comptage / décomptage .....                         | 49        |

| 4.6.4                      | Fonctionnement synchrone ou asynchrone .....        | 49        |

| 4.6.4.1                    | Compteur synchrone .....                            | 49        |

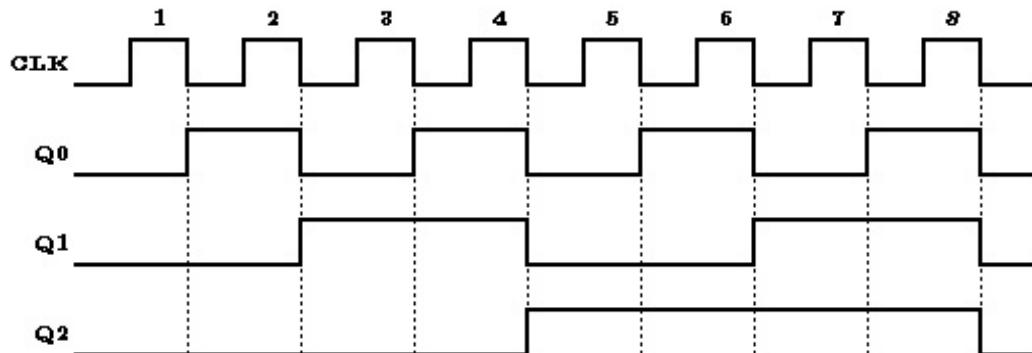

| 4.6.4.2                    | Compteur asynchrone .....                           | 49        |

| 4.6.5                      | Type de fonctionnement .....                        | 49        |

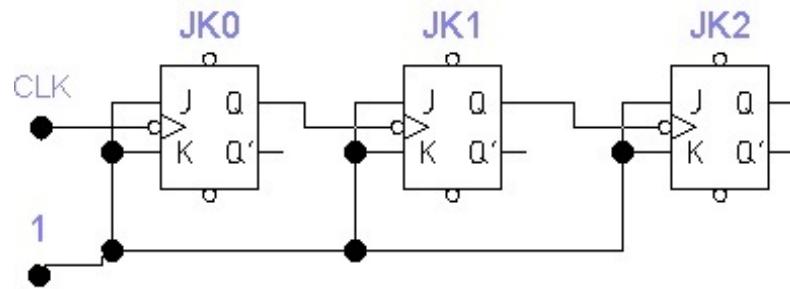

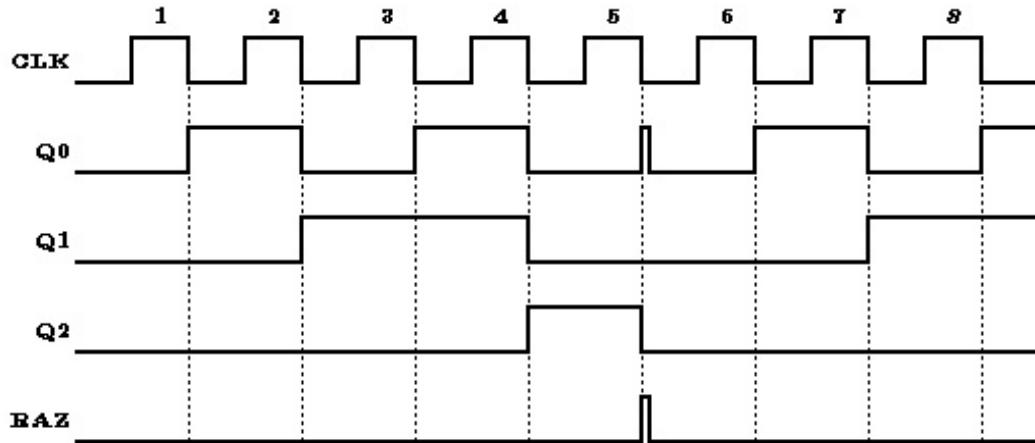

| 4.6.6                      | Synthèse des compteurs asynchrones .....            | 49        |

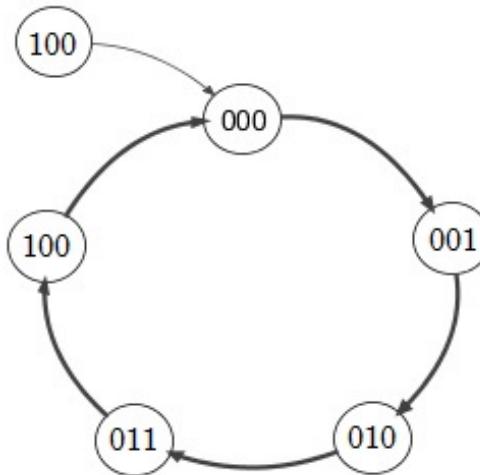

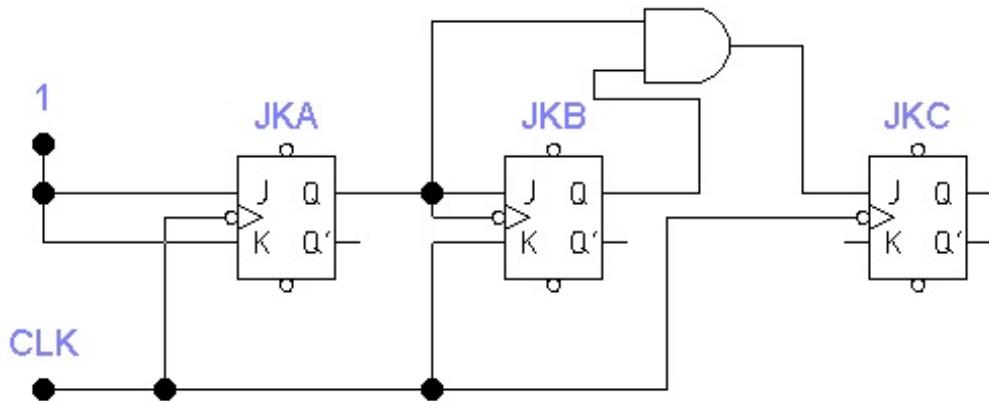

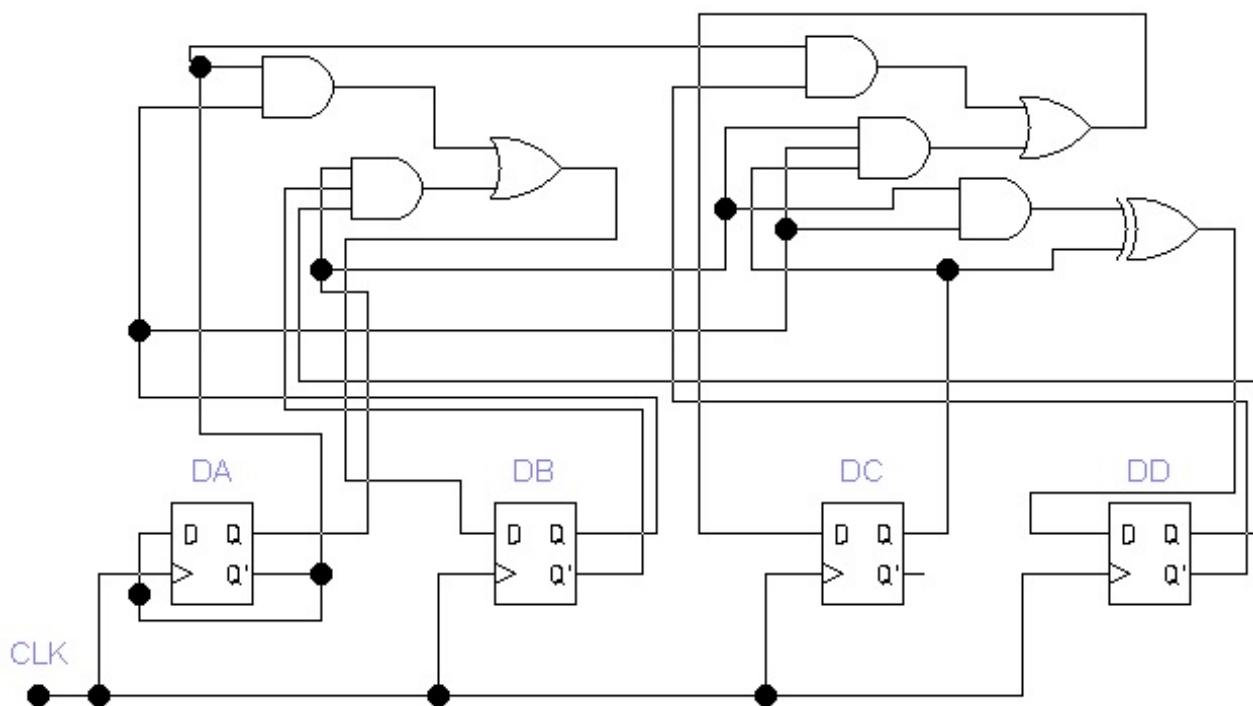

| 4.6.7                      | Synthèse des compteurs synchrones .....             | 51        |

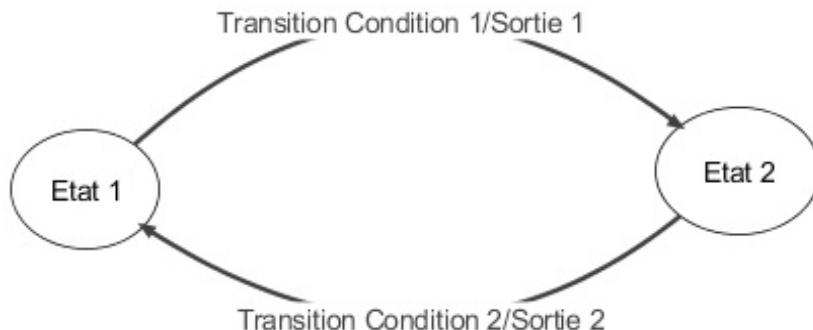

| <b>5.</b>                  | <b>MACHINES À ÉTATS FINIS .....</b>                 | <b>56</b> |

| 5.1                        | Définition .....                                    | 56        |

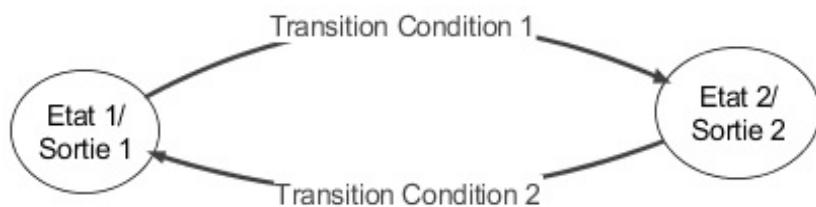

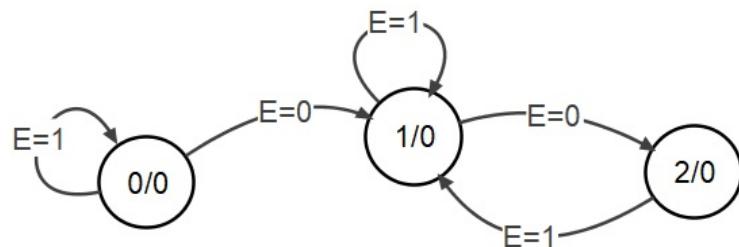

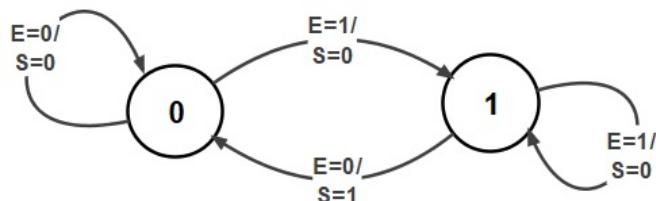

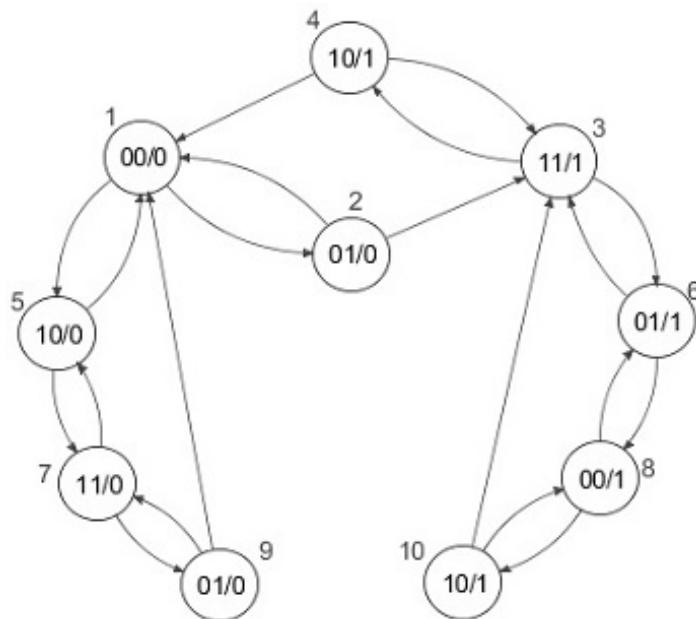

| 5.2                        | Types des machines Séquentielles .....              | 57        |

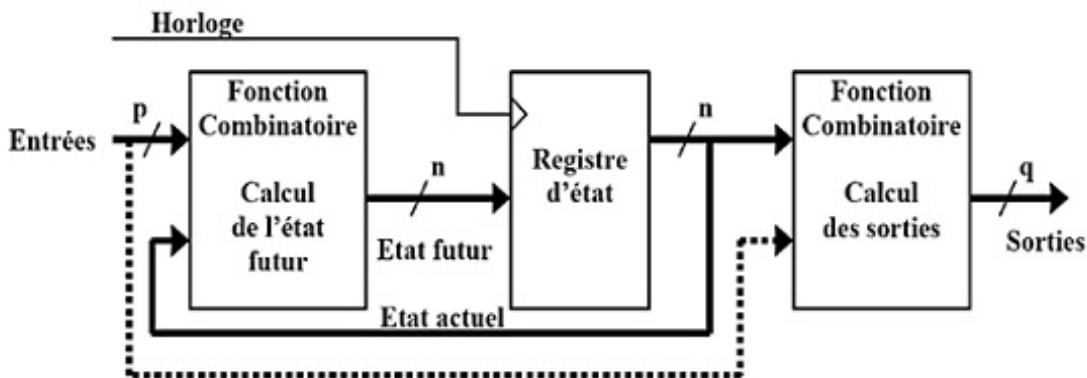

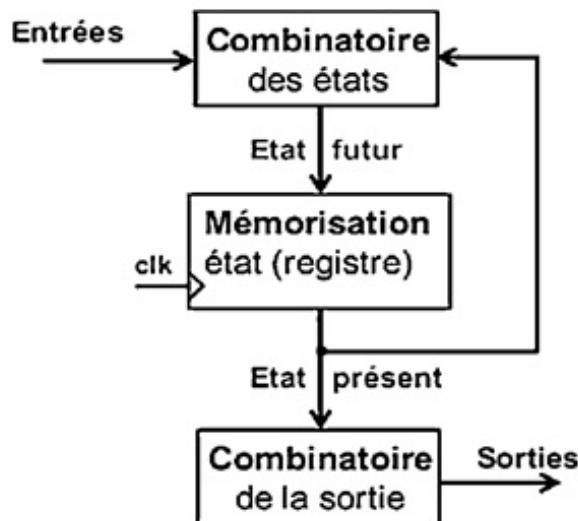

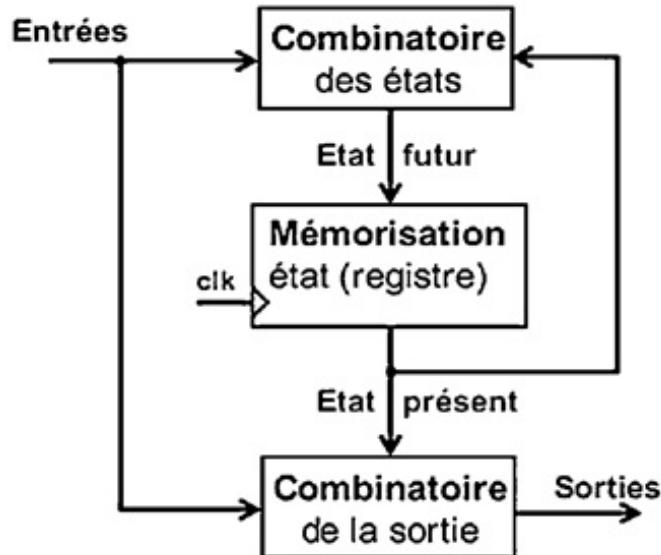

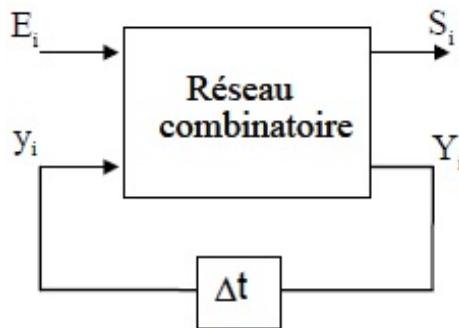

| 5.3                        | Les machines synchrones à nombre d'états fini ..... | 57        |

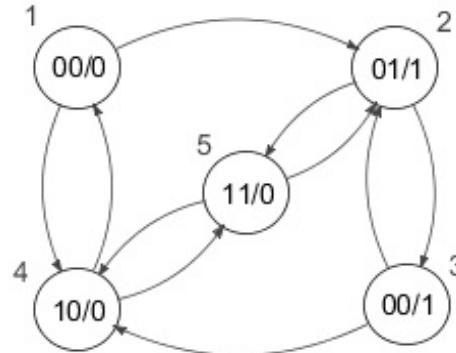

| 5.4                        | Différentes Architectures de La FSM .....           | 58        |

| 5.4.1                      | Machine de Moore .....                              | 58        |

| 5.4.2                      | Machine de Mealy .....                              | 59        |

| 5.5                        | Comparaison entre les deux machines .....           | 60        |

| <b>6.</b>                  | <b>LES SYSTÈMES SÉQUENTIELS ASYNCHRONES .....</b>   | <b>61</b> |

| 6.1                        | Introduction .....                                  | 61        |

| 6.2                        | Structure d'un système séquentiel asynchrone .....  | 61        |

| 6.3                        | But d'un système séquentiel asynchrone .....        | 61        |

| 6.4                        | La synthèse par la méthode d'Hoffman .....          | 62        |

| 6.5                        | Commande d'un moteur .....                          | 62        |

| 6.5.1                      | Le graphe d'états .....                             | 63        |

| 6.5.2                      | Matrice primitive des états .....                   | 63        |

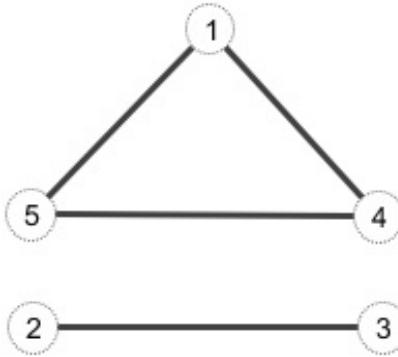

| 6.5.3                      | Polygone de liaison .....                           | 64        |

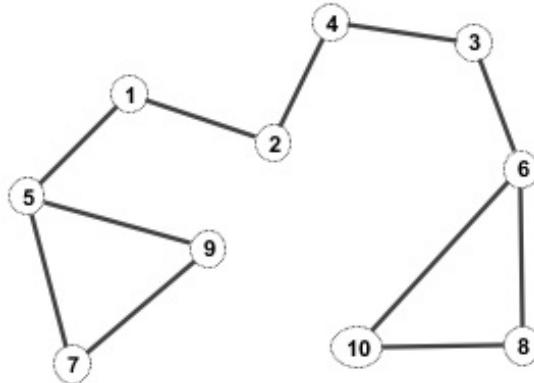

| 6.5.4                      | Table d'états réduite .....                         | 64        |

| 6.5.5                      | Variables secondaires .....                         | 65        |

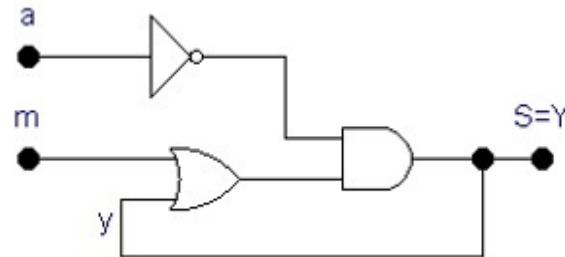

| 6.5.6                      | Equation de la fonction de sortie $S$ .....         | 65        |

| 6.6                        | Ouverture d'une serrure électronique .....          | 66        |

| <b>BIBLIOGRAPHIE .....</b> | <b>69</b>                                           |           |

# Avant propos

Ce cours intitulé *Systèmes Numériques 01*, est conçu aux étudiants de deuxième année d'ingénierat en électronique, électrotechnique et automatique. Et peut être utilisé par les étudiants ingénieurs en informatique. Le module est décortiqué en deux parties, à savoir la logique combinatoire et celle séquentielle, dont chaque partie est subdivisée en trois chapitres.

Le chapitre 1 est consacré aux systèmes logiques combinatoires, en commençant par la représentation numérique de l'information, le comportement des circuits combinatoires et la simplification des fonctions logiques, ainsi qu'une présentation de quelques systèmes séquentiels complexes.

Le chapitre 2 est dédié au comportement des circuits séquentiels, à savoir les bascules, les registres à décalage et les compteurs. Et on terminera par la synthèse des systèmes séquentiels asynchrones.

Le module en question comporte une charge hebdomadaire de 15 semaines, telle que, 01 cours de 01H30, 01 TD de 01H30 et 01 TP de 03H00. Son évaluation finale sera effectuée de la manière suivante :

- Devoirs maison, Assiduité, et interrogation sur 30% ;

- Travaux pratiques sur 30% ;

- Examen final, noté sur 40%.

**Première partie**

**Logique combinatoire**

# Chapitre 1

## Représentation Numérique de l'information

### 1.1 Représentation des nombres

La représentation universelle utilisée dans notre vie quotidienne est la numérotation dite décimale. Elle contient des nombres constitués d'une série de chiffres et comprenant parfois un point ou une virgule.

Et puisque l'ordinateur est devenu une machine indispensable dans nos jours, alors il est parfois pratique d'utiliser d'autres bases que la base 10 ; les plus utilisées sont les bases 2, 8 et 16 qui conduisent à manipuler des nombres représentés en binaire, en octal ou en hexadécimal.

Dans un système de base  $k$ , il faudrait  $k$  symboles différents pour exprimer les chiffres de 0 à  $k-1$ .

Les nombres exprimés en octal constitués de huit chiffres : 0 1 2 3 4 5 6 7.

Pour exprimer un nombre en hexadécimal, on utilise en plus des dix chiffres décimaux les six premières lettres de l'alphabet romain. Donc, en hexadécimal les nombres sont exprimés avec les symboles : 0 1 2 3 4 5 6 7 8 9 A B C D E F.

### 1.2 Systèmes de numérations

La numération est une manière qui consiste à représenter un nombre  $A$  dans un système de base quelconque  $B$  : Décimal, Hexadécimal, Octal, Binaire, ...

$$178,25_{10} = 1.10^2 + 7.10^1 + 8.10^0 + 2.10^{-1} + 5.10^{-2}$$

$$10111,01_2 = 1.2^4 + 0.2^3 + 1.2^2 + 1.2^1 + 1.2^0 + 0.2^{-1} + 1.2^{-2}, \text{ d'où :}$$

$$N_B = a_{n-1} \cdot B^{n-1} + a_{n-2} \cdot B^{n-2} + \dots + a_0 \cdot B^0 + a_{-1} \cdot B^{-1} + \dots$$

Sachant que  $B$  représente la base,  $a_{n-1}$  le digit et  $B^{n-1}$  la puissance.

### 1.3 Conversion d'un système de numération

#### 1.3.1 Conversion de la base B vers 10

Afin de convertir un nombre en base B vers une autre base 10, on multiplie chaque chiffre du nombre représenté en base B par la puissance de B correspondante, puis effectuer la somme de ses produits. L'exemple suivant montre une conversion de la base 2 vers la base 10 :

$$\begin{aligned} 11011,101_2 &= 1 \cdot 2^4 + 1 \cdot 2^3 + 0 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0 + 1 \cdot 2^{-1} + 0 \cdot 2^{-2} + 1 \cdot 2^{-3} \\ &= 16 + 8 + 0 + 2 + 1 + 0,5 + 0 + 0,125 \\ &= 27,62510 \end{aligned}$$

#### 1.3.2 Conversion de la base 10 vers B

Il existe deux méthodes pour convertir un nombre en base B vers une autre base 10 :

##### 1.3.2.1 1<sup>ère</sup> Méthode (Soustraction successive)

Une 1<sup>ère</sup> méthode consiste à soustraire la plus grande puissance de B d'une manière successive, avec B = 2 :

$$\left. \begin{array}{l} 363_{10} = 2^8 + 7 \\ 107 = 2^6 + 43 \\ 43 = 2^5 + 11 \\ 11 = 2^3 + 3 \\ 3 = 2^1 + 1 \\ 1 = 2^0 \end{array} \right\} \quad \begin{array}{l} 363_{10} = 2^8 + 2^6 + 2^5 + 2^3 + 2^1 + 2^0 \\ = 101101011_2 \end{array}$$

##### 1.3.2.2 2<sup>ème</sup> Méthode (Division)

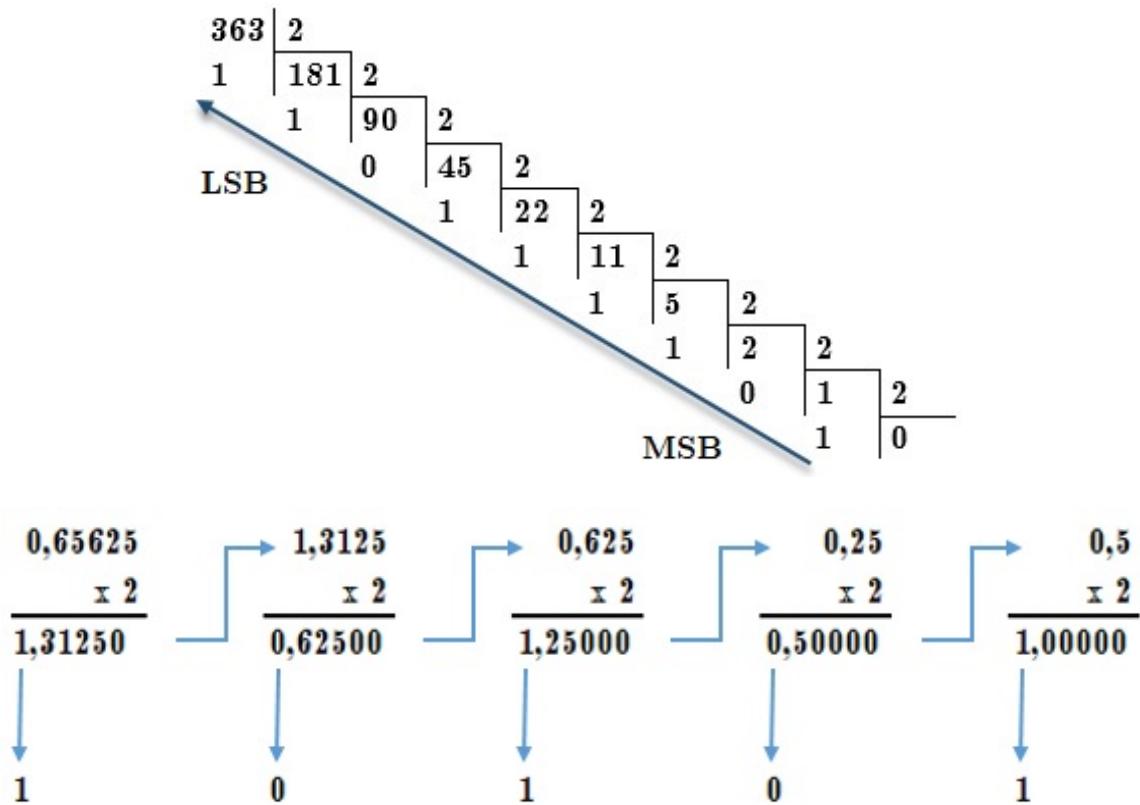

La 2<sup>ème</sup> méthode consiste le nombre par la base B autant de fois que nécessaire pour obtenir le quotient nul, puis on écrit le reste dans l'ordre inverse où ils ont été obtenus, de la manière suivante : Il vient,  $363_{10} = 101111011_2$ .

**NB :** Le bit le plus à droite est appelé le bit le plus significatif ou LSB (Least Significant Bit), alors que celui le plus à gauche est appelé le bit le plus moins significatif ou MSB (Most Significant Bit).

Or, pour convertir un nombre décimal fractionnaire en base binaire, il suffit de multiplier le nombre en question par 2, et à chaque opération on garde le premier nombre après la virgule.

**Exemple :**  $0,65625_{10} = 0,10101_2$

### 1.3.3 Généralisation de la conversion en puissance de 2

#### 1.3.3.1 Conversion de la base $2^n$ vers la base n

La méthode consiste à convertir chaque chiffre du nombre  $2^n$  en base 2, puis on juxtapose les résultats.

**Exemple :**  $475_8 = ?_2$ .  $B = 8 = 2^3 \rightarrow 3$  bits,

|     |     |     |

|-----|-----|-----|

| 4   | 7   | 5   |

| 100 | 111 | 101 |

Donc,  $475_8 = 100\ 111\ 101_2$ .

#### 1.3.3.2 Conversion de la base 2 vers la base $2^n$

Dans la conversion inverse, on découpe le nombre en tranches de n éléments binaires chacun.

**Exemple :**  $11\ 000\ 111\ 011\ 011\ 001_2 = ?_8$ .  $B = 8 = 2^3 \rightarrow 3$  bits,

|    |     |     |     |     |     |

|----|-----|-----|-----|-----|-----|

| 11 | 000 | 111 | 011 | 011 | 001 |

| 3  | 0   | 7   | 3   | 3   | 1   |

Donc,  $11\ 000\ 111\ 011\ 011\ 001_2 = 307331_8$ .

#### 1.3.3.3 Conversion de la base 'i' vers la base 'j'

- Si 'i' et 'j' sont tous les deux des puissances de 2, on utilise la base 2 comme base de relais :

$$i \rightarrow j$$

**Exemple :**  $E8A_{16} = ?_8$ ,

|      |      |      |

|------|------|------|

| E    | 8    | A    |

| 1110 | 1000 | 1010 |

$$E8A_{16} = 111\ 010\ 001\ 010_2 = ?_8, \quad \begin{array}{|c|c|c|c|} \hline & 111 & 010 & 001 & 010 \\ \hline & 7 & 2 & 1 & 2 \\ \hline \end{array}$$

D'où,  $E8A_{16} = 7212_8$ .

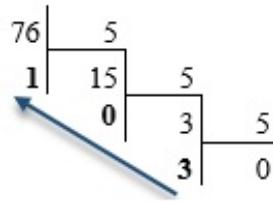

o Si ‘i’ et ‘j’ ne sont pas de la puissance de 2, dans ce cas on utilise la base 10 comme base de relais.

**Exemple :**  $136_7 = ?_5$

$$136_7 = 1 \cdot 7^2 + 3 \cdot 7^1 + 6 \cdot 7^0 = 76_{10}.$$

$$136_7 = 76_{10} = ?_5.$$

D'où,  $136_7 = 301_5$ .

### 1.3.4 L'arithmétique binaire

Quand un calculateur effectue une opération arithmétique, deux contraintes interviennent :

1. Les circuits arithmétiques travaillent sur des nombres qui ont toujours le même format (longueur).

Prenant l'exemple d'un codage de 8 bits, où le nombre **10111** doit être complété par des zéros :

**00010111** ;

2. Les circuits manipulent seulement deux nombres à la fois. Donc, pour obtenir  $S = X + Y + Z$ ,

on effectue :  $S = X + Y$  puis  $S = S + Z$ .

#### 1.3.4.1 Les opérations

Les mêmes règles de calculs s'appliquent dans un système de numération. L'arithmétique binaire ressemble à celle des nombres décimaux.

| $a$ | $b$ | $Add.$ | $R_+$ | $Soust.$ | $R_-$ | $Prod.$ | $R_x$ |

|-----|-----|--------|-------|----------|-------|---------|-------|

| 0   | 0   | 0      | 0     | 0        | 0     | 0       | 0     |

| 0   | 1   | 1      | 0     | 1        | 1     | 0       | 0     |

| 1   | 0   | 1      | 0     | 1        | 0     | 0       | 0     |

| 1   | 1   | 0      | 1     | 0        | 0     | 1       | 0     |

### 1.4 Codage des entiers

Le code est une correspondance entre un ensemble des objets et un autre ensemble des symboles.

Ce code traduit le langage humain en langage machine.

### 1.4.1 Les codes pondérés

Ce sont ceux qu'on utilise dans les opérations arithmétiques, on peut citer : le code binaire et ses dérivées (Octal, Hexadécimal, ...) et le code DCB (Décimal Codé Binaire).

#### 1.4.1.1 Codage binaire pur

C'est une représentation d'un nombre dans le système de numération binaire. D'où avec 8 bits on peut coder tous les entiers positifs dans un intervalle compris entre 0000 0000 et 1111 1111, c'est-à-dire entre 0 et 255. Donc, avec  $n$  bits on peut coder tous les entiers entre 0 et  $2^n-1$ . Sachant que cette représentation n'est pas valable pour les nombres négatifs.

#### 1.4.1.2 Codage DCB (Décimal Codé Binaire)

Cette représentation permet de coder chaque chiffre d'un nombre décimal sur 4 bits, comme suit :

|      |      |      |      |      |

|------|------|------|------|------|

| 1    | 0    | 4    | 9    | 7    |

| 0001 | 0000 | 0100 | 1001 | 0111 |

#### 1.4.1.3 Codage binaire signé

Afin d'utiliser un additionneur comme soustracteur, il est impératif de représenter convenablement les nombres négatifs de la manière suivante :

$$A - B = A + (-B)$$

Dans une telle représentation, le bit le plus à gauche indique le signe. On utilise 0 pour indiquer un nombre positif et 1 pour nombre négatif. Dans ce cas et pour  $n$  bits, on ne peut représenter que les entiers compris entre  $-(2^n-1)$  et  $(2^n-1)$ . Et on note que la représentation du 0 n'est pas unique.

**Exemple :**  $11111111_2$  représentent  $-127$  et  $01101100_2$  représente  $+108$ .

Soit à calculer  $-6+7$

$$\begin{array}{r}

0000\ 0111 \quad (+7) \\

+\ 1000\ 0110 \quad (-6) \\

\hline

=\ 1000\ 1101 \quad (-13)

\end{array}$$

On constate que l'addition binaire n'est pas souvent valable pour les nombres négatifs en utilisant la représentation binaire signée si on ne prend pas en considération à part le bit signe.

#### 1.4.1.4 Codage en complément à 1 (Complément restreint)

Les entiers positifs sont représentés comme celle du binaire signé. On obtient le complément à 1 (C1) d'un nombre entier  $x$  en inversant tous les bits de la représentation de  $x$ , c'est-à-dire remplacer les 0 par des 1 et inversement.

**Exemple :**  $x = 010011_2 \rightarrow C1(x) = 101100_2$ .

Si  $n$  est le nombre d'éléments binaires de  $x$ , alors :

$$x + C1(x) = 2^n - 1$$

$$\begin{array}{r} x = 1101_2 \\ + C1(x) = 0010_2, \text{ d'où} \\ \hline = 1111_2 \end{array}$$

$$-x = C1(x) + 1 - 2^n$$

Ce qui montre que le  $C1(x) + 1$  représente le nombre négatif de  $x$ , à condition de ne pas en tenir compte du chiffre de poids  $2^n$ , comme le montre l'exemple suivant pour  $n = 4$  :

$$\begin{array}{r} x = +13 \quad \dots 000 \ 1101_2 \\ C1(x) + 1 \quad \dots 111 \ 0011_2 \\ \hline \dots 000 \ 0000_2 \end{array}$$

#### 1.4.1.5 Codage en complément à 2 (Complément vrai)

Les nombres positifs sont représentés de la même manière que celle du binaire. Afin de représenter les nombres négatifs, on part du complément à 1 puis on ajoute 1, appelé complément à 2 (C2).

$$-x = C1(x) + 1 = C2(x)$$

D'où avec  $n$  bits on peut coder les nombres compris entre  $-2^{n-1}$  et  $(2^{n-1} - 1)$ .

**Exemple :**

$$x = 13_{10} = 1101_2 \rightarrow C2(x) = 0010_2 + 1 = 0011_2. \text{ Or, } C2(C2(x)) = 1100_2 + 1 = 1101_2 = 13_{10}.$$

- o La représentation du nombre 0 est unique.

- o La somme de 2 nombres de signes opposés est toujours correcte.

- o La somme de 2 nombres de même signe n'est juste que si le résultat est de même signe.

**Exemple :**

$$\begin{array}{rccccc} 11111100 & (-4) & & 01111110 & (+126) & & 11000000 & (-64) \\ + 00000110 & (+6) & + & 00000010 & (+2) & + & 10111111 & (-65) \\ \hline 1 : 00000010 & (+2) & & 10000000 & (-128) & 1 : & 01111111 & (+127) \\ \text{Avec retenue} & & \text{Sans} & \text{retenue mais} & & \text{Avec} & \text{retenue mais} \\ & & & \text{avec} & & & \text{avec} \\ & & & \text{débordement} & & & \text{débordement} \end{array}$$

D'après les exemples ci-dessus, on peut constater que la retenue (Carry) n'est pas suffisante pour indiquer le débordement de calcul (Overflow). Ce dernier n peut être représenté correctement sur un nombre n de bits.

### 1.4.2 Les codes non pondérés

#### 1.4.2.1 Codage excédent 3

On obtient ce code en décalant vers le haut de trois lignes le code DCB (voir la table ci-bas).

#### 1.4.2.2 Codage binaire réfléchi (GRAY)

Dans ce code chaque deux termes successifs ne diffèrent que par un seul bit, on dit que les termes sont adjacents.

| Nombre | Code DCB | Excédent 3 | Nombre | Code Binaire | Code GRAY |

|--------|----------|------------|--------|--------------|-----------|

| 0      | 0000     | 0011       | 0      | 000          | 000       |

| 1      | 0001     | 0100       | 1      | 001          | 001       |

| 2      | 0010     | 0101       | 2      | 010          | 011       |

| 3      | 0011     | 0110       | 3      | 011          | 010       |

| 4      | 0100     | 0111       | 4      | 100          | 110       |

| 5      | 0101     | 1000       | 5      | 101          | 111       |

| 6      | 0110     | 1001       | 6      | 110          | 101       |

| 7      | 0111     | 1010       | 7      | 111          | 100       |

| 8      | 1000     | 1011       |        |              |           |

| 9      | 1001     | 1100       |        |              |           |

## 1.5 Représentation des nombres réels

Les nombres réels sont utilisés dans les systèmes numériques car ils permettent une variété de calculs. Ils peuvent être représentés avec une virgule fixe ou flottante. La représentation en virgule fixe permet de coder une plage fixe de nombres et d'effectuer des calculs rapides, tandis que la codification de nombres de différents ordres de grandeur est plus facile avec une représentation en virgule flottante.

### 1.5.1 Virgule fixe

L'idée de la virgule fixe serait d'utiliser un entier et de déplacer ainsi sa virgule d'un nombre fixe de position, ce qui revient à multiplier la base par une puissance bien définie. Par exemple en base 10 avec un décalage de 3, 123.456 serait représenté par 123456 et 1.23456 par 1234. D'où on passe d'un entier à un réel par multiplication de  $10^{-3}$ .

### 1.5.2 Virgule flottante

L'inconvénient de la représentation en virgule fixe est qu'on ne peut représenter des réels grands ou petits, comme par exemple la constante de Planck ( $\hbar \approx 1,0545718 \times 10^{-34} \text{ J.s}$ ), le nombre d'Avogadro ( $N_A = 6,02214076 \times 10^{23} \text{ mol}^{-1}$ ), .... D'où l'idée de faire varier la position de la virgule, d'où le nom de représentation à virgule flottante.

Cette représentation peut être considérée comme une notation scientifique pour les systèmes numériques. Un certain nombre de représentations en virgule flottante ont été proposées pour répondre aux exigences de nombreuses applications. Un nombre décimal  $N$  peut être quantifié et exprimé sous forme de virgule flottante comme suit :

$$N_{10} = (-1)^S \cdot M \cdot B^E$$

Où  $S$  est le bit de signe,  $M$  est la mantisse,  $B$  est la base et  $E$  est l'exposant. La mantisse est généralement normalisée et correspond à un nombre commençant par un chiffre différent de zéro, comme dans le cas des représentations numériques suivantes :

| Nombre              | Représentation           |

|---------------------|--------------------------|

| $-1234.57_{10}$     | $-1.23457 \times 10^3$   |

| $0.0000071539_{10}$ | $+7.1539 \times 10^{-6}$ |

| $100010100_2$       | $1.00010100 \times 2^8$  |

## Chapitre 2

# Algèbre de Boole et fonctions logiques

### 2.1 Définition

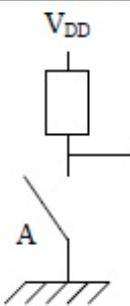

La mise en œuvre pratique de systèmes logiques est, la plupart du temps, basée sur la technologie des circuits logiques électroniques. L'algèbre de base ressemble sous certains aspects à l'algèbre classique. C'est un ensemble de variables à deux états de valeur de vérité *vrai* (1) ou *faux* (0), correspondant à successivement à deux valeurs de tension  $0v$  et  $5v$  et munie d'un nombre fini d'opérateurs : *Non*, *Et*, *Ou*, ...

La manipulation de ses variables dites booléennes en fonction de ses opérateurs donne aussi une des fonctions booléennes.

**Exemple :** Un circuit électronique ouvert est une variable booléenne *vraie* (1) et vice versa.

### 2.2 Opérations et fonctions de base de l'algèbre de Boole

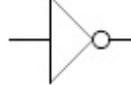

#### 2.2.1 Fonction à une seule variable

L'inverseur est un opérateur qui ne porte que sur une seule variable d'entrée,  $S = \bar{A}$ .

| Table de vérité                                                                                                                                                        | Montage       | Symbole traditionnel | Symbole normalisé |   |   |   |                                                                                     |                                                                                      |                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|-------------------|---|---|---|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <table border="1"><thead><tr><th>A</th><th>S = <math>\bar{A}</math></th></tr></thead><tbody><tr><td>0</td><td>1</td></tr><tr><td>1</td><td>0</td></tr></tbody></table> | A             | S = $\bar{A}$        | 0                 | 1 | 1 | 0 |  |  |  |

| A                                                                                                                                                                      | S = $\bar{A}$ |                      |                   |   |   |   |                                                                                     |                                                                                      |                                                                                       |

| 0                                                                                                                                                                      | 1             |                      |                   |   |   |   |                                                                                     |                                                                                      |                                                                                       |

| 1                                                                                                                                                                      | 0             |                      |                   |   |   |   |                                                                                     |                                                                                      |                                                                                       |

#### 2.2.2 Fonction à deux variables

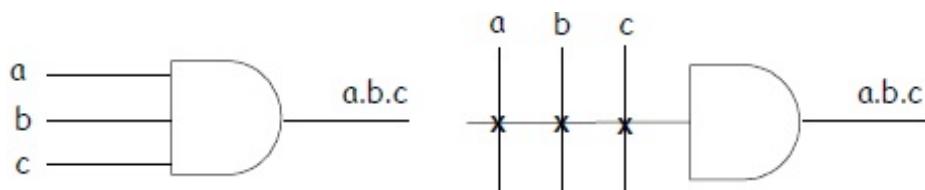

##### 2.2.2.1 Opérateur ET (AND)

Si on prend  $A$  et  $B$  comme des variables d'entrée, alors  $S = A \cdot B$ .  $S$  est vraie si  $A$  et  $B$  sont vraies.

| Table de vérité                                                                                                                                                                                                                                                                                 | Montage | Symbole traditionnel | Symbole normalisé |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|-------------------|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|

| <table border="1"> <thead> <tr> <th>A</th><th>B</th><th><math>S = A \cdot B</math></th></tr> </thead> <tbody> <tr><td>0</td><td>0</td><td>0</td></tr> <tr><td>0</td><td>1</td><td>0</td></tr> <tr><td>1</td><td>0</td><td>0</td></tr> <tr><td>1</td><td>1</td><td>1</td></tr> </tbody> </table> | A       | B                    | $S = A \cdot B$   | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |  |  |  |

| A                                                                                                                                                                                                                                                                                               | B       | $S = A \cdot B$      |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                               | 0       | 0                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                               | 1       | 0                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                               | 0       | 0                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                               | 1       | 1                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

### 2.2.2.2 Opérateur OU (OR)

Si  $A$  et  $B$  sont les variables d'entrée, alors  $S = A + B$ .  $S$  est vraie si  $A$  ou  $B$  sont vraies.

| Table de vérité                                                                                                                                                                                                                                                                             | Montage | Symbole traditionnel | Symbole normalisé |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|-------------------|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|

| <table border="1"> <thead> <tr> <th>A</th><th>B</th><th><math>S = A + B</math></th></tr> </thead> <tbody> <tr><td>0</td><td>0</td><td>0</td></tr> <tr><td>0</td><td>1</td><td>1</td></tr> <tr><td>1</td><td>0</td><td>1</td></tr> <tr><td>1</td><td>1</td><td>1</td></tr> </tbody> </table> | A       | B                    | $S = A + B$       | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |  |  |  |

| A                                                                                                                                                                                                                                                                                           | B       | $S = A + B$          |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                           | 0       | 0                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                           | 1       | 1                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                           | 0       | 1                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                           | 1       | 1                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

### 2.2.2.3 Opérateur Non ET (NAND)

Si  $A$  et  $B$  sont les variables d'entrée, alors  $S = \overline{A \cdot B}$ .  $S$  est fausse si  $A$  et  $B$  sont vraies. Le *NAND* est l'inverseur du *AND*.

| Table de vérité                                                                                                                                                                                                                                                                                            | Montage | Symbole traditionnel       | Symbole normalisé          |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------|----------------------------|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|

| <table border="1"> <thead> <tr> <th>A</th><th>B</th><th><math>S = \overline{A \cdot B}</math></th></tr> </thead> <tbody> <tr><td>0</td><td>0</td><td>1</td></tr> <tr><td>0</td><td>1</td><td>1</td></tr> <tr><td>1</td><td>0</td><td>1</td></tr> <tr><td>1</td><td>1</td><td>0</td></tr> </tbody> </table> | A       | B                          | $S = \overline{A \cdot B}$ | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |  |  |  |

| A                                                                                                                                                                                                                                                                                                          | B       | $S = \overline{A \cdot B}$ |                            |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                          | 0       | 1                          |                            |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                          | 1       | 1                          |                            |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                          | 0       | 1                          |                            |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                          | 1       | 0                          |                            |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

### 2.2.2.4 Opérateur Non OU (NOR)

Si  $A$  et  $B$  sont les variables d'entrée, alors  $S = \overline{A + B}$ .  $S$  est fausse si  $A$  ou  $B$  sont vraies. Le *NOR* est l'inverseur du *OR*.

| Table de vérité                                                                                                                                                                                                                                                                                            | Montage | Symbole traditionnel   | Symbole normalisé      |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|------------------------|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|

| <table border="1"> <thead> <tr> <th>A</th><th>B</th><th><math>S = \overline{A + B}</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>1</td></tr> <tr> <td>0</td><td>1</td><td>0</td></tr> <tr> <td>1</td><td>0</td><td>0</td></tr> <tr> <td>1</td><td>1</td><td>0</td></tr> </tbody> </table> | A       | B                      | $S = \overline{A + B}$ | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |  |  |  |

| A                                                                                                                                                                                                                                                                                                          | B       | $S = \overline{A + B}$ |                        |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                          | 0       | 1                      |                        |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                          | 1       | 0                      |                        |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                          | 0       | 0                      |                        |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                          | 1       | 0                      |                        |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

### 2.2.2.5 Opérateur OU Exclusif (XOR)

Cet opérateur n'est pas un opérateur de base car il peut être réalisé avec les portes décrites ci-dessus. Si  $A$  et  $B$  sont les variables d'entrée, alors  $S = A \oplus B = A\overline{B} + \overline{A}B$ .  $S$  est vraie si  $A \neq B$ .

| Table de vérité                                                                                                                                                                                                                                                                                      | Montage | Symbole traditionnel | Symbole normalisé |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|-------------------|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|

| <table border="1"> <thead> <tr> <th>A</th><th>B</th><th><math>S = A \oplus B</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>0</td></tr> <tr> <td>0</td><td>1</td><td>1</td></tr> <tr> <td>1</td><td>0</td><td>1</td></tr> <tr> <td>1</td><td>1</td><td>0</td></tr> </tbody> </table> | A       | B                    | $S = A \oplus B$  | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |  |  |  |

| A                                                                                                                                                                                                                                                                                                    | B       | $S = A \oplus B$     |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                    | 0       | 0                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                    | 1       | 1                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                    | 0       | 1                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                    | 1       | 0                    |                   |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

### 2.2.2.6 Opérateur Non OU Exclusif (XNOR)

Si  $A$  et  $B$  sont les variables d'entrée, alors  $S = \overline{A \oplus B} = AB + \overline{A}B$ .  $S$  est vraie si  $A = B$ .

| Table de vérité                                                                                                                                                                                                                                                                                                 | Montage | Symbole traditionnel        | Symbole normalisé           |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|-----------------------------|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|

| <table border="1"> <thead> <tr> <th>A</th><th>B</th><th><math>S = \overline{A \oplus B}</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>1</td></tr> <tr> <td>0</td><td>1</td><td>0</td></tr> <tr> <td>1</td><td>0</td><td>0</td></tr> <tr> <td>1</td><td>1</td><td>1</td></tr> </tbody> </table> | A       | B                           | $S = \overline{A \oplus B}$ | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |  |  |  |

| A                                                                                                                                                                                                                                                                                                               | B       | $S = \overline{A \oplus B}$ |                             |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                               | 0       | 1                           |                             |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 0                                                                                                                                                                                                                                                                                                               | 1       | 0                           |                             |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                               | 0       | 0                           |                             |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

| 1                                                                                                                                                                                                                                                                                                               | 1       | 1                           |                             |   |   |   |   |   |   |   |   |   |   |   |   |  |  |  |

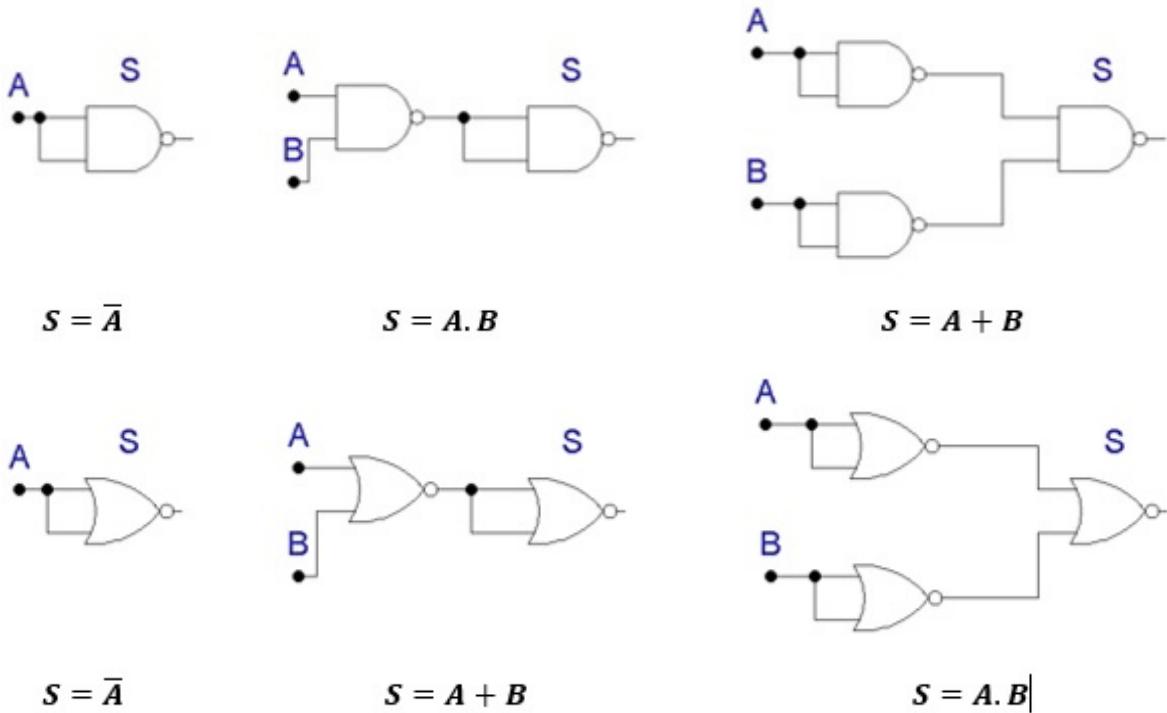

### 2.2.2.7 Les portes universelles

Le *NAND* et le *NOR* sont toutes les deux des portes universelles car elles permettent de réaliser n'importe quel opérateur logique élémentaires.

Le même type de montage peut être réalisé avec des portes *NOR*.

### 2.3 Axiomes ou lois fondamentales de l'algèbre de Boole

Les lois fondamentales de l'algèbre de BOOLE pourraient être vérifiées avec des tables de vérités et en testant toutes les possibilités. Les lois sont les suivantes :

|                        |                                                                                        |

|------------------------|----------------------------------------------------------------------------------------|

| Commutativité          | $A \cdot B = B \cdot A$                                                                |

| Associativité          | $A \cdot (B \cdot C) = (A \cdot B) \cdot C$<br>$A + (B + C) = (A + B) + C$             |

| Distributivité         | $A \cdot (B + C) = A \cdot B + A \cdot C$<br>$A + (B \cdot C) = (A + B) \cdot (A + C)$ |

| Idempotence            | $A \cdot A = 1$<br>$A + A = A$                                                         |

| Complémentarité        | $A \cdot \bar{A} = 0$<br>$A + \bar{A} = 1$                                             |

| Identités remarquables | $1 \cdot A = A$<br>$1 + A = 1$<br>$0 \cdot A = 0$<br>$0 + A = A$                       |

### 2.4 Relations de base dans l'algèbre de Boole

$$1- \quad x \cdot y + x \cdot \bar{y} = x$$

$$1^{\circ}- \quad (x + y) \cdot (x + \bar{y}) = x$$

**Preuve :**  $x.y + x.\bar{y} = x.(y + \bar{y}) = x.1 = x$

$$2- \quad x + x.y = x$$

$$2^\circ - \quad x.(x + y) = x$$

**Preuve :**  $x + x.y = x.(1 + y) = x.1 = x$

$$3- \quad x + \bar{x}.y = x + y$$

$$3^\circ - \quad x.(\bar{x} + y) = x.y$$

**Preuve :**  $x + \bar{x}.y = x + x.y + \bar{x}.y = x + y.(x + \bar{x}) = x + y.1 = x + y$

## 2.5 Théorèmes de MORGAN

**Théorème 1 (01)** *La négation d'un produit de variables est égale à la somme des négations :*

$$\overline{x.y.z} = \bar{x} + \bar{y} + \bar{z}$$

**Théorème 2 (02)** *La négation d'une somme de variables est égale au produit des négations :*

$$\overline{x + y + z} = \bar{x}.\bar{y}.\bar{z}$$

## 2.6 Représentation des fonctions booléennes

### 2.6.1 Mintermes / Maxtermes

- On appelle Minterme, le produit logique  $P_i$  de toutes les variables d'entrée intervenant dans une forme directe ou complémentée.

- On appelle Maxterme, la somme logique  $S_i$  de toutes les variables d'entrée intervenant dans une forme directe ou complémentée.

**Exemple :**

$$F_1 = \frac{abc + a\bar{b}\bar{c} + a\bar{b}\bar{c}}{P_0} \quad F_2 = \frac{(a + b + c)}{S_0} \cdot (a + \bar{b} + c) \cdot (a + \bar{b} + \bar{c}).$$

### 2.6.2 Formes canoniques

Soit une fonction  $F$ , la 1<sup>ère</sup> forme canonique de cette fonction est la réunion *OU* des Mintermes destinés aux 1 logiques de la fonction :

$$F(x_n, x_{n-1}, \dots, x_0) = \bigcup_{i=0} P_i$$

La 2<sup>ème</sup> forme canonique de la fonction  $F$  est L'intersection *ET* des Mintermes destinés aux 0 logiques de la fonction :

$$F(x_n, x_{n-1}, \dots, x_0) = \bigcap_{i=0} S_i$$

**Exemple :** Soit une fonction  $F$  en fonction de trois variables booléennes  $a$ ,  $b$  et  $c$ . La fonction est vraie si et seulement si la somme de ses variables d'entrées est un nombre pair. La table de vérité de  $F$  est donnée comme suit :

| a | b | c | F | P <sub>i</sub>          | S <sub>i</sub>                | $\bar{F}$ |

|---|---|---|---|-------------------------|-------------------------------|-----------|

| 0 | 0 | 0 | 1 | $\bar{a}\bar{b}\bar{c}$ | $a + b + c$                   | 0         |

| 0 | 0 | 1 | 0 | $\bar{a}\bar{b}c$       | $a + b + \bar{c}$             | 1         |

| 0 | 1 | 0 | 0 | $\bar{a}b\bar{c}$       | $a + \bar{b} + c$             | 1         |

| 0 | 1 | 1 | 1 | $\bar{a}bc$             | $a + \bar{b} + \bar{c}$       | 0         |

| 1 | 0 | 0 | 0 | $a\bar{b}\bar{c}$       | $\bar{a} + b + c$             | 1         |

| 1 | 0 | 1 | 1 | $a\bar{b}c$             | $\bar{a} + b + \bar{c}$       | 0         |

| 1 | 1 | 0 | 1 | $ab\bar{c}$             | $\bar{a} + \bar{b} + c$       | 0         |

| 1 | 1 | 1 | 0 | $abc$                   | $\bar{a} + \bar{b} + \bar{c}$ | 1         |

D'après la table de vérité, la fonction  $F$  peut s'écrire sous la 1<sup>ère</sup> forme canonique comme suit :

$$F(a, b, c) = \bar{a}\bar{b}\bar{c} + \bar{a}\bar{b}c + a\bar{b}\bar{c} + a\bar{b}c + abc$$

Afin de passer de la 1<sup>ère</sup> forme à la 2<sup>ème</sup> forme canonique, on prend en compte les combinaisons pour lesquelles  $F$  vaut 0.

$$\bar{F}(a, b, c) = 1 = \bar{a}\bar{b}\bar{c} + \bar{a}\bar{b}\bar{c} + a\bar{b}\bar{c} + abc, \text{ donc :}$$

$$F(a, b, c) = 0 = \overline{\bar{a}\bar{b}\bar{c} + \bar{a}\bar{b}\bar{c} + a\bar{b}\bar{c} + abc}, \text{ et d'après le théorème de MORGAN, il vient :}$$

$$F(a, b, c) = \overline{\bar{a}\bar{b}\bar{c}.\bar{a}\bar{b}\bar{c}.\bar{a}\bar{b}\bar{c}.abc}, \text{ d'où}$$

$$F(a, b, c) = (a + b + \bar{c}).(a + \bar{b} + c).(\bar{a} + b + c).(\bar{a} + \bar{b} + \bar{c})$$

### 2.6.3 La représentation numérique

Pour représenter numériquement la fonction  $F$ , on utilise directement 1 table de vérité :

$$F(a, b, c) = \sum(0, 4, 5, 7)$$

$\sum$  : représente le symbole de la somme logique. Les nombres entre parenthèse correspondent aux équivalents décimaux des combinaisons des variables d'entrée pour lesquelles la fonction vaut 1.

La représentation numérique équivalente est obtenue en prenant en compte les zéros de la fonction :

$$F(a, b, c) = \prod(1, 2, 3, 6)$$

$\prod$  : représente le symbole du produit logique. Les nombres entre parenthèse correspondent aux équivalents décimaux des combinaisons des variables d'entrée pour lesquelles la fonction vaut 0.

### 2.6.4 Représentation par le diagramme de Karnaugh

Cette représentation correspond à  $2^n$  cases. Chaque case de la table est associée à une combinaison des variables d'entrée et elle comprend la valeur de la fonction  $F$  en fonction des variables d'entrée. Les diagrammes (tables) de Karnaugh pour  $n=2, 3$  et  $4$  sont illustrés successivement comme suit :

| <b>a</b> | <b>b</b> | 0 | 1 |

|----------|----------|---|---|

| 0        |          |   |   |

| 1        |          |   |   |

| <b>a</b> | <b>bc</b> | 00 | 01 | 11 | 10 |

|----------|-----------|----|----|----|----|

| 0        |           |    |    |    |    |

| 1        |           |    |    |    |    |

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        |           |    |    |    |    |

| 01        |           |    |    |    |    |

| 11        |           |    |    |    |    |

| 10        |           |    |    |    |    |

Le diagramme de Karnaugh comprend une disposition particulière qui dit que deux cases voisines correspondent à des combinaisons adjacentes, d'où des combinaisons des diffèrent que par l'état d'une seule variable. Les cases du diagramme de pour lesquels la fonction vaut 0 sont laissées vides, sinon on met 1, comme illustré dans la table ci-bas.

Pour  $n = 4$ , les cases adjacentes de la combinaison 1000 sont 0000, 1100, 1010 et 1001.

**Exemple :** Soit  $F(a, b, c, d) = \bar{a}bcd + a\bar{b}c + ab\bar{c} + b$

$$\bar{a}bcd : abcd = 0111$$

$$ab\bar{c} : \forall d, abcd = 1001/1000$$

$$a\bar{b}c : \forall d, abcd = 1010/1011$$

$$b : \forall (a, c, d), \dots$$

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        |           |    |    |    |    |

| 01        | 1         | 1  | 1  | 1  |    |

| 11        | 1         | 1  | 1  | 1  |    |

| 10        |           |    |    | 1  | 1  |

## 2.6.5 Simplification des fonctions booléennes

Afin de simplifier une fonction à partir de la table de Karnaugh, on procède comme suit :

- o Regrouper toutes les cases adjacentes pour lesquelles la fonction vaut 1 ;

- o Le nombre de 1 dans les groupements doit être en puissance de 2 ;

- o Eliminer les variables qui changent d'état et retenir ainsi celles qui conservent leur valeur lorsqu'on passe d'une case à l'autre.

*Les doubles* : Groupement de  $2 = 2^1$ .

*Les quadruplets* : Groupement de  $4 = 2^2$ .

*Les octets* : Groupement de  $8 = 2^3$ .

**Remarque 3** Une case peut être utilisée plusieurs fois, en raison de :  $a + a + a + \dots + a = a$

| <b>a</b> | <b>bc</b> | 00 | 01 | 11 | 10 |

|----------|-----------|----|----|----|----|

| 0        | 0         | 1  | 1  |    |    |

| 1        | 1         |    |    |    |    |

| <b>a</b> | <b>bc</b> | 00 | 01 | 11 | 10 |

|----------|-----------|----|----|----|----|

| 0        | 0         | 1  |    |    | 1  |

| 1        | 1         |    |    |    |    |

| <b>a</b> | <b>bc</b> | 00 | 01 | 11 | 10 |

|----------|-----------|----|----|----|----|

| 0        | 0         |    |    |    | 1  |

| 1        | 1         |    |    |    | 1  |

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        | 0         | 1  | 1  |    |    |

| 01        | 1         |    |    |    |    |

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        | 0         |    |    |    |    |

| 01        | 1         | 1  | 1  | 1  | 1  |

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        | 0         | 1  |    |    | 1  |

| 01        | 1         |    |    |    |    |

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        | 0         |    |    | 1  | 1  |

| 01        | 1         |    |    | 1  | 1  |

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        | 0         | 1  |    |    | 1  |

| 01        | 1         |    |    |    | 1  |

| <b>ab</b> | <b>cd</b> | 00 | 01 | 11 | 10 |

|-----------|-----------|----|----|----|----|

| 00        | 0         |    |    | 1  | 1  |

| 01        | 1         |    |    | 1  | 1  |

| cd<br>ab | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       | 1  |    |    | 1  |

| 01       |    |    | 1  |    |

| 11       |    |    | 1  |    |

| 10       | 1  | 1  | 1  | 1  |

$$F = a\bar{b} + \bar{b}\bar{d} + bcd$$

| cd<br>ab | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       | 1  |    |    |    |

| 01       | 1  | 1  | 1  |    |

| 11       | 1  | 1  |    | 1  |

| 10       | 1  |    |    |    |

$$F = b\bar{c} + \bar{c}\bar{d} + \bar{a}bd + ab\bar{d}$$

| cd<br>ab | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    |    |    | 1  |

| 01       | 1  | 1  | 1  |    |

| 11       |    | 1  | 1  |    |

| 10       |    |    | 1  |    |

$$F = bd + \bar{a}b\bar{c} + acd + \bar{a}\bar{b}c\bar{d}$$

| cd<br>ab | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    |    | 1  |    |

| 01       | 1  | 1  | 1  | 1  |

| 11       | 1  | 1  |    |    |

| 10       |    |    |    |    |

$$F = b\bar{c} + \bar{a}b + \bar{a}cd$$

## 2.6.6 Les règles importantes pour lire un diagramme de Karnaugh

- Entourer tous les 1 impérativement ;

- Les cases vides (ou les 0) ne sont pas prises en considération ;

- Le 1 peut être entouré plusieurs fois.

Les exemples ci-bas montrent différents groupements d'une fonction  $F(a, b, c, d)$  :

## 2.6.7 Les fonctions incomplètement définies

Dans ce type de fonctions qu'on verra plus en détail ultérieurement, nous allons placer des  $\phi$  dans les cases correspondantes aux combinaisons interdites et les 1 dans les cases correspondantes à la fonction.

| cd<br>ab | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    | 1  |    |    |

| 01       |    | 1  | 1  | 1  |

| 11       | 1  | 1  | 1  |    |

| 10       |    |    | 1  |    |

$$F = \bar{a}\bar{c}d + ab\bar{c} + acd + \bar{a}bc$$

| cd<br>ab | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       |    | 1  |    |    |

| 01       |    | 1  | 1  | 1  |

| 11       |    |    |    | 1  |

| 10       | 1  | 1  |    | 1  |

$$F = \bar{a}\bar{c}d + ab\bar{c} + ac\bar{d} + \bar{a}bc$$

Lors de la simplification, on va attribuer  $\phi$  à la valeur 1 ou 0, afin d'obtenir les groupements les plus étendus. Voir l'exemple suivant :

| <b>cd</b><br><b>ab</b> | 00     | 01     | 11     | 10     |

|------------------------|--------|--------|--------|--------|

| 00                     | $\phi$ | $\phi$ | $\phi$ |        |

| 01                     | 1      | 1      |        | $\phi$ |

| 11                     | $\phi$ | $\phi$ |        |        |

| 10                     | 1      | 1      | 1      | $\phi$ |

$$F = \bar{b}d + b\bar{c}$$

### 2.6.8 Synthèse des systèmes combinatoires

La méthode à suivre afin d'extraire les équations d'un circuit combinatoire consiste à effectuer successivement les étapes suivantes :

- o Extraire la table de vérité à partir du problème en question, c'est-à-dire :

- Déterminer le nombre  $n$  de variables d'entrée, d'où on aura  $2^n$  combinaisons possibles ;

- Déterminer le nombre de variables de sorties ;

- Analyser chacune des combinaisons des variables d'entrée.

- o Simplifier séparément chaque fonction de sortie par le diagramme (table) de Karnaugh ;

- o Etablir le schéma du circuit combinatoire à partir du système d'équation résultant.

#### Exemple :

Un distributeur de boisson permet de livrer aux consommateur de l'eau, la grenadine à l'eau et la menthe à l'eau. Mais il ne doit pas obtenir de : la grenadine seule, la menthe seule et la grenadine à la menthe.

La façade du distributeur comporte trois boutons :

$$e : \text{ L'Eau} \quad g : \text{ La Grenadine} \quad m : \text{ La Menthe}$$

Déterminer la commande d'ouverture du robinet  $R$  du distributeur en déduire le logigramme correspondant en fonction seulement des portes  $NAND$ .

#### Solution :

- o Table de vérité et simplification par le diagramme de Karnaugh (voir la figure ci-bas) :

| $e$ | $m$ | $g$ | $R$ |

|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   |

| 0   | 0   | 1   | 0   |

| 0   | 1   | 0   | 0   |

| 0   | 1   | 1   | 0   |

| 1   | 0   | 0   | 1   |

| 1   | 0   | 1   | 1   |

| 1   | 1   | 0   | 1   |

| 1   | 1   | 1   | 0   |

|           |    |    |    |    |

|-----------|----|----|----|----|

| <b>mg</b> | 00 | 01 | 11 | 10 |

| <b>e</b>  |    |    |    |    |

| <b>00</b> |    |    |    |    |

| <b>01</b> | 1  | 1  | 1  | 1  |

- Simplification par la table de Karnaugh :

$$R = e \cdot \bar{m} + e \cdot \bar{g} \implies R = e \cdot (\bar{m} + \bar{g})$$

- Logigramme en fonction des portes *NAND* :

$$R = e \cdot \overline{\overline{m + g}} = e \cdot \overline{m} \cdot \overline{g} \implies R = \overline{\overline{e} \cdot \overline{m} \cdot \overline{g}}$$

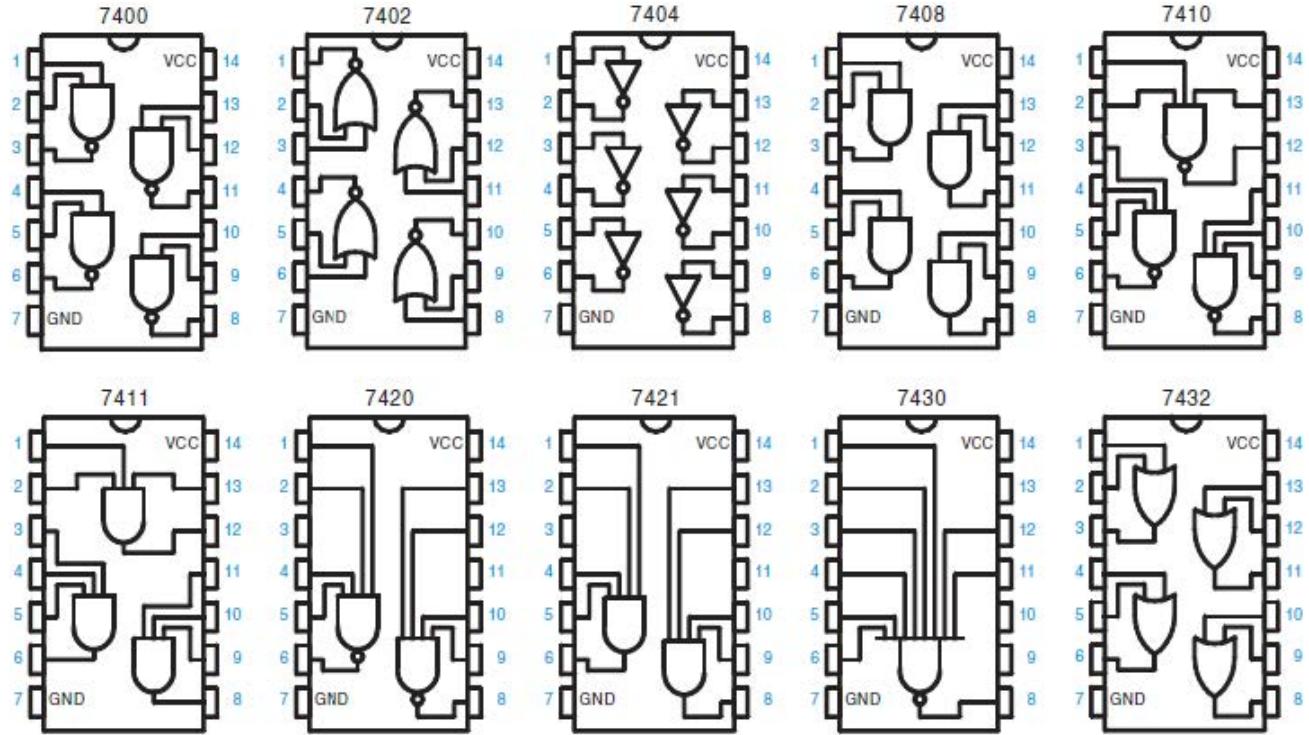

## 2.7 Quelques circuits intégrés logiques usuels

# Chapitre 3

## Circuits combinatoires usuels

### 3.1 Objectif

Dans certains cas, il est avantageux de concevoir des systèmes composés d'un ensemble de sous-systèmes identiques mis en cascade. Dans le présent chapitre nous examinerons les principaux circuits combinatoires usuels à savoir :

- Les circuits arithmétiques ;

- Les circuits de transcodage ;

- Les circuits d'aiguillage ;

- Systèmes séquentiels complexes.

### 3.2 Les circuits arithmétiques

#### 3.2.1 L'additionneur binaire

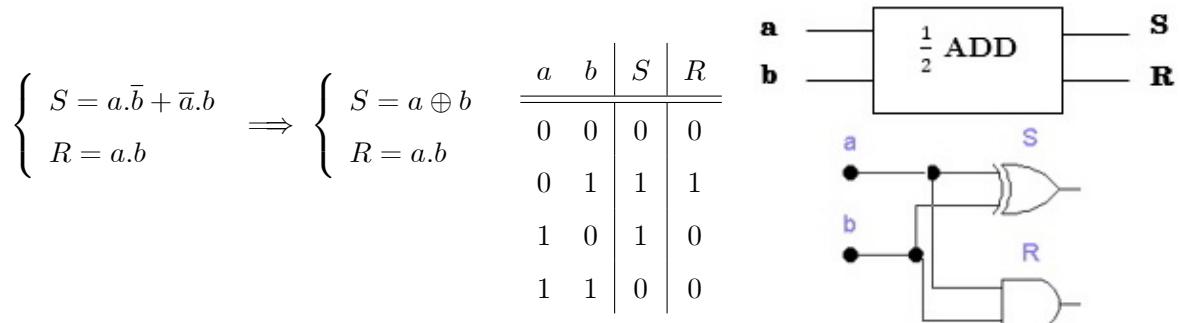

##### 3.2.1.1 Le demi-additionneur ( $\frac{1}{2}$ ADD)

Il représente une addition simple de deux bits  $a$  et  $b$ . On obtient donc une somme  $S = a + b$  et une éventuelle retenue  $R$ . Et d'après la table de vérité illustrée ci-bas, on obtient les équations de  $S$  et  $R$  comme suit :

##### 3.2.1.2 L'additionneur complet (ADD)

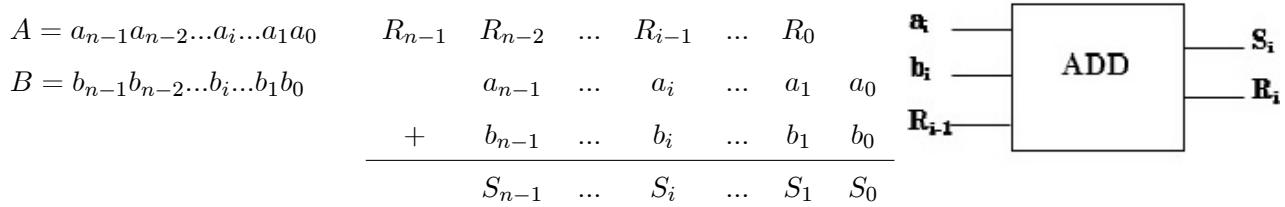

Considérons le cas de deux nombres binaires  $A$  et  $B$  de  $n$  bits chacun. La différence avec le demi-additionneur, c'est qu'il va y avoir une retenue précédente comme représenté ci-après :

La table de vérité et les diagrammes de Karnaugh correspondant à la somme et la retenue sont illustrés comme suit :

| $a_i$ | $b_i$ | $R_{i-1}$ | $S_i$ | $R_i$ |

|-------|-------|-----------|-------|-------|

| 0     | 0     | 0         | 0     | 0     |

| 0     | 0     | 1         | 1     | 0     |

| 0     | 1     | 0         | 1     | 0     |

| 0     | 1     | 1         | 0     | 1     |

| 1     | 0     | 0         | 1     | 0     |

| 1     | 0     | 1         | 0     | 1     |

| 1     | 1     | 0         | 0     | 1     |

| 1     | 1     | 1         | 1     | 1     |

**$S_i$**

| $a_i$ | $b_i$ | $R_{i-1}$ | 00 | 01 | 11 | 10 |

|-------|-------|-----------|----|----|----|----|

| 0     | 0     | 0         |    | 1  |    | 1  |

| 0     | 1     | 0         | 1  |    | 1  |    |

| 1     | 0     | 0         |    |    | 1  |    |

| 1     | 1     | 0         |    | 1  | 1  | 1  |

**$R_i$**

| $a_i$ | $b_i$ | $R_{i-1}$ | 00 | 01 | 11 | 10 |

|-------|-------|-----------|----|----|----|----|

| 0     | 0     | 0         |    |    | 1  |    |

| 0     | 1     | 0         |    |    | 1  |    |

| 1     | 0     | 0         |    |    | 1  |    |

| 1     | 1     | 0         |    | 1  | 1  | 1  |

D'après la table de vérité, les formes canoniques de  $S_i$  et  $R_i$  sont données comme suit :

- $R_i = \overline{a_i}b_iR_{i-1} + a_i\overline{b_i}R_{i-1} + a_i b_i \overline{R_{i-1}} + a_i b_i R_{i-1} \implies R_i = R_{i-1}(\overline{a_i}b_i + a_i\overline{b_i}) + a_i b_i(R_{i-1} + \overline{R_{i-1}})$ ,

il vient :  $R_i = a_i b_i + R_{i-1}(a_i \oplus b_i)$

- $S_i = \overline{a_i}\overline{b_i}R_{i-1} + \overline{a_i}b_i\overline{R_{i-1}} + a_i\overline{b_i}R_{i-1} + a_i b_i R_{i-1} \implies S_i = R_{i-1}(\overline{a_i}\overline{b_i} + a_i b_i) + \overline{R_{i-1}}(\overline{a_i}b_i + a_i\overline{b_i})$

$\implies S_i = R_{i-1}(\overline{a_i} \oplus b_i) + \overline{R_{i-1}}(a_i \oplus b_i)$ , il vient :

$$S_i = a_i \oplus b_i \oplus R_{i-1}$$

D'où le logigramme,

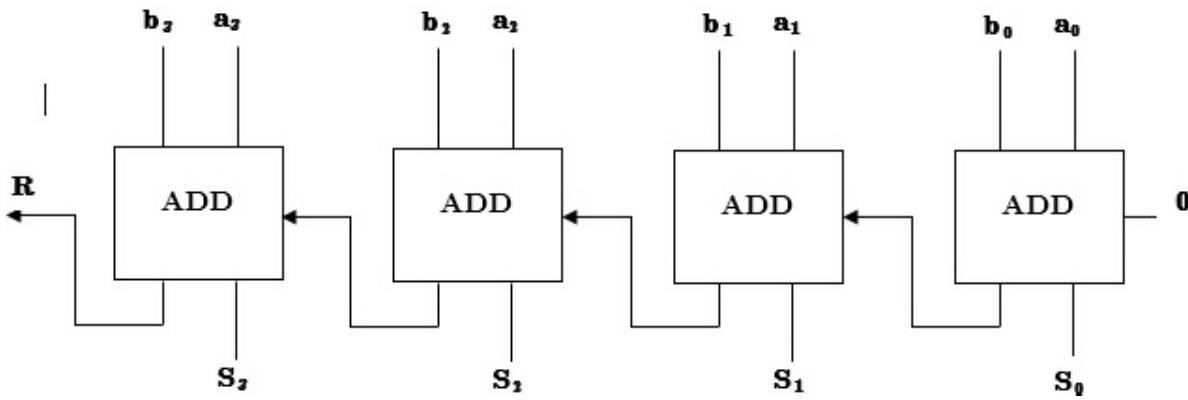

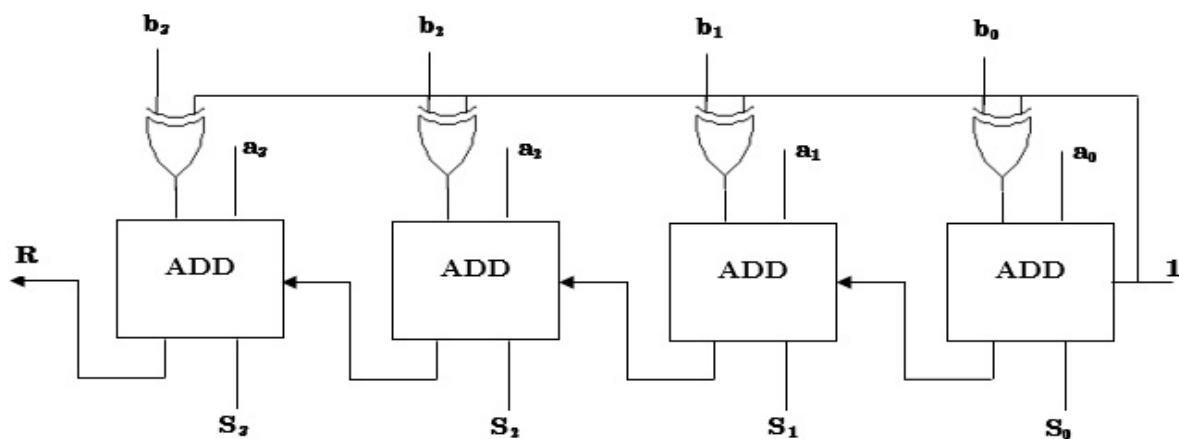

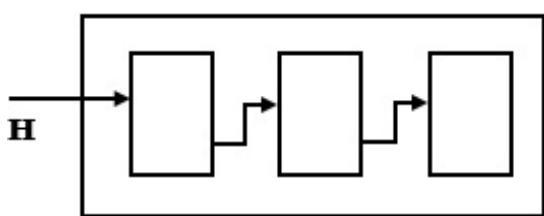

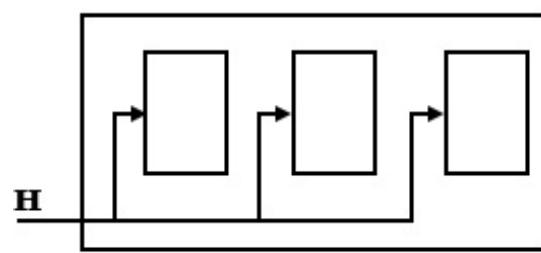

Le dispositif qui réalise l'addition de deux nombres binaires  $A$  et  $B$  de  $n$  bits chacun est constitué d'un demi-additionneur au rang 0 et de  $(n - 1)$  additionneurs complets mis en cascade, comme le montre la figure suivante :

### 3.2.2 Le soustracteur binaire

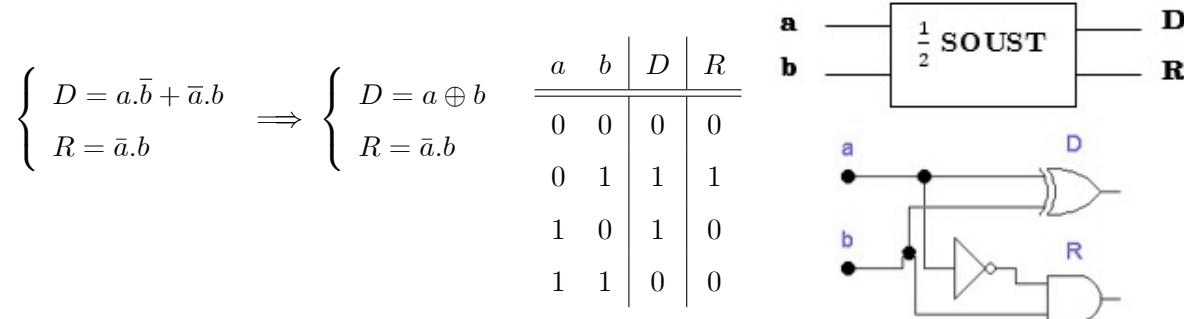

#### 3.2.2.1 Le demi-soustracteur ( $\frac{1}{2}$ SOUST)

Ressemblant au cas de la demi-addition. C'est la soustraction simple de deux bits  $a$  et  $b$ . On obtient donc une différence  $D = a - b$  et une éventuelle retenue  $R$ . Et d'après la table de vérité illustrée ci-bas, on obtient les équations de  $D$  et  $R$  comme suit :

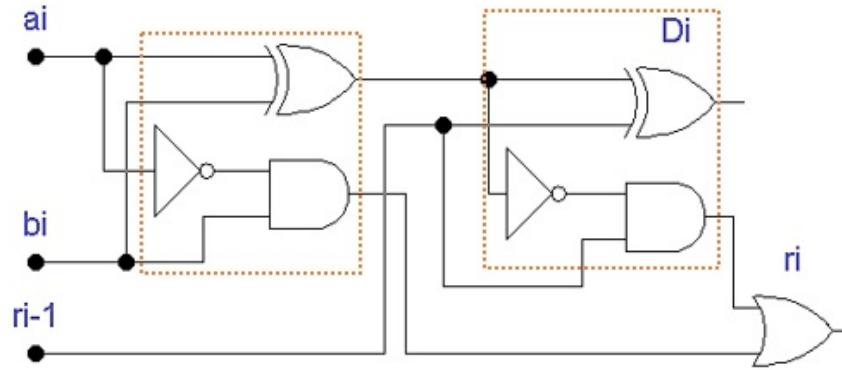

#### 3.2.2.2 Le soustracteur complet (SOUST)

Considérons le cas de deux nombres binaires  $A$  et  $B$  de  $n$  bits chacun. Les résultats sont la différence  $D_i = a_i - b_i - r_{i-1}$  et la retenue  $r_i$ , données comme suit :

| $a_i$ | $b_i$ | $r_{i-1}$ | $D_i$ | $r_i$ |

|-------|-------|-----------|-------|-------|

| 0     | 0     | 0         | 0     | 0     |

| 0     | 0     | 1         | 1     | 1     |

| 0     | 1     | 0         | 1     | 1     |

| 0     | 1     | 1         | 0     | 1     |

| 1     | 0     | 0         | 1     | 0     |

| 1     | 0     | 1         | 0     | 0     |

| 1     | 1     | 0         | 0     | 0     |

| 1     | 1     | 1         | 1     | 1     |

D'après la table de vérité :

- $r_i = \overline{a_i b_i} r_{i-1} + \overline{a_i b_i} \overline{r_{i-1}} + \overline{a_i b_i} r_{i-1} + a_i b_i r_{i-1} \implies r_i = a_i \overline{b_i} (\overline{r_{i-1}} + r_{i-1}) + r_{i-1} (\overline{a_i b_i} + a_i b_i)$ , il vient :  $r_i = a_i \overline{b_i} + r_{i-1} (\overline{a_i} \oplus b_i)$

- $D_i = S_i$  c'est-à-dire que :  $D_i = a_i \oplus b_i \oplus R_{i-1}$

D'où le logigramme,

Cet additionneur est capable de traiter des nombres négatifs représentés en complément à deux comme indiqué dans le *chapitre 01*. Il reste à déterminer comment traiter la soustraction ?

On remarque que l'expression  $x - y$  est équivalente à celle  $x + (-y)$ . Au 1<sup>er</sup> chapitre, on a vu, que pour avoir l'opposé d'un nombre il suffit d'inverser chacun de ses bits, puis on l'additionne à 1 au résultat. Il reste donc à calculer l'expression  $x + \overline{y} + 1$ . Afin de calculer  $\overline{y}$ , on inverse chaque position de  $y$  avant d'arriver à l'additionneur, mais comment ajouter 1 par la suite ? Cette opération semble nécessiter encore un additionneur. Heureusement, nous avons une entrée (retenue précédente) de la position 0 qui n'est pas actuellement utilisée. Or donner la valeur 1 à cette entrée additionne 1 au résultat entier. Le circuit complet pour la soustraction est présenté sur la figure.

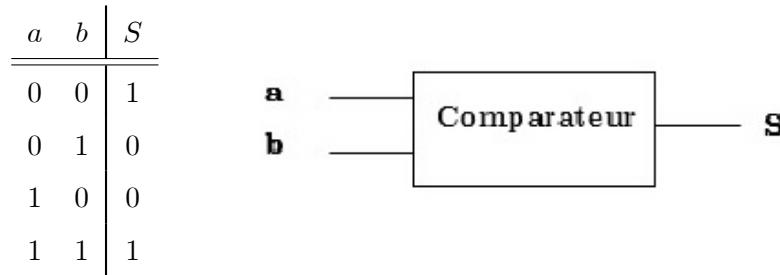

### 3.2.3 Les comparateurs

C'est un circuit à deux entrées d'informations binaires  $a$  et  $b$  en plus d'une sortie  $S$ , indiquant si ses deux informations sont égales ou non. Et d'après la table de vérité on en déduit que l'opérateur  $XNOR$  représente le comparateur binaire élémentaire de deux bits.

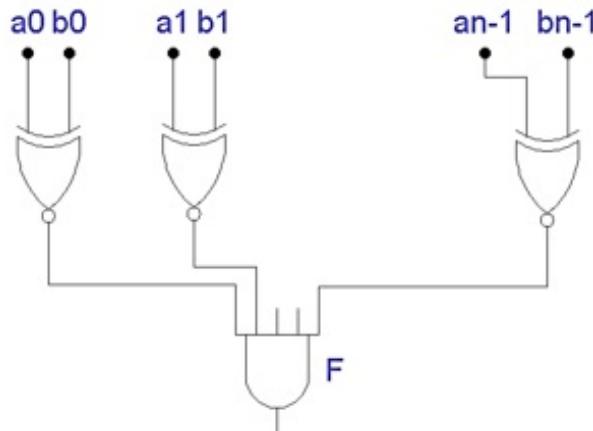

Or, si on considère que  $A$  et  $B$  sont deux informations de  $n$  bits chacun telle que :

$$\begin{cases} A = a_{n-1}a_{n-2} \dots a_i \dots a_1a_0 \\ B = b_{n-1}b_{n-2} \dots b_i \dots b_1b_0 \end{cases}$$

Afin de satisfaire l'égalité  $A = B$ , il est impératif que tous les bits des deux informations en question du même rang soient égaux, sinon  $A \neq B$ .

$$\text{D'où } F = \overline{a_0 \oplus b_0} \cdot \overline{a_1 \oplus b_1} \dots \overline{a_{n-1} \oplus b_{n-1}}$$

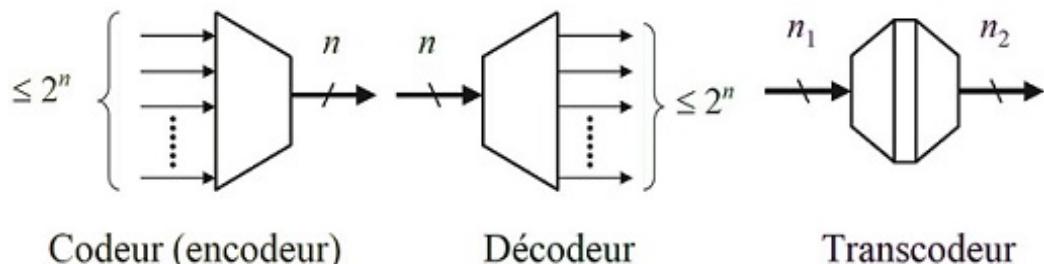

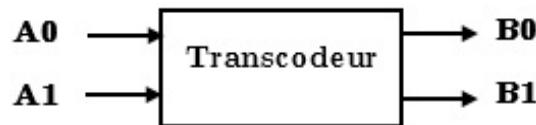

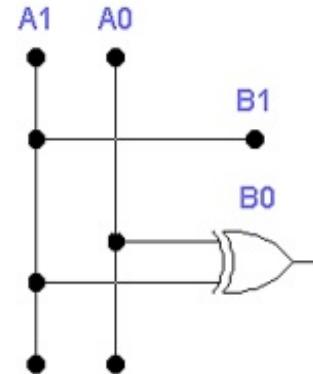

### 3.3 Les circuits de transcodage

Un opérateur de transcodage est un circuit qui converti une information présente en entrée et exprimée dans un code A en son équivalent dans un autre code B, telle que :

$$\begin{cases} I_{cA} = A_1A_2A_3\dots \\ I_{cB} = B_1B_2B_3\dots \end{cases}$$

D'où il faut établir les fonctions suivantes :

$$\left\{ \begin{array}{l} B_1 = f(A_1, A_2, A_3, \dots) \\ B_2 = f(A_1, A_2, A_3, \dots) \\ B_3 = f(A_1, A_2, A_3, \dots) \\ \dots \\ \dots \end{array} \right.$$

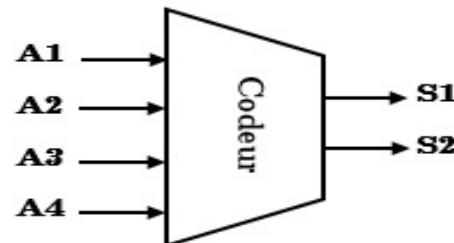

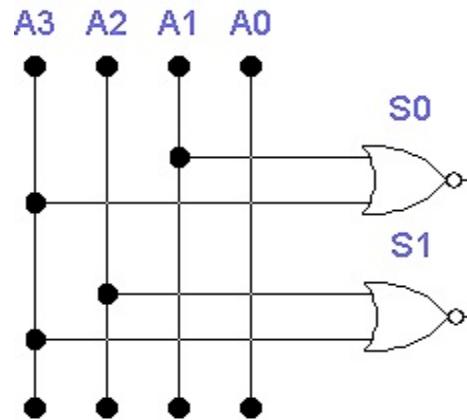

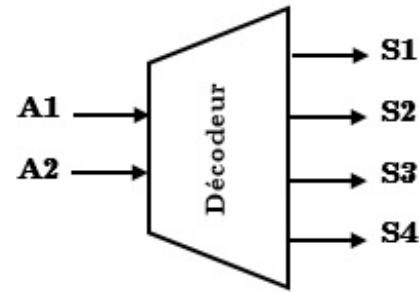

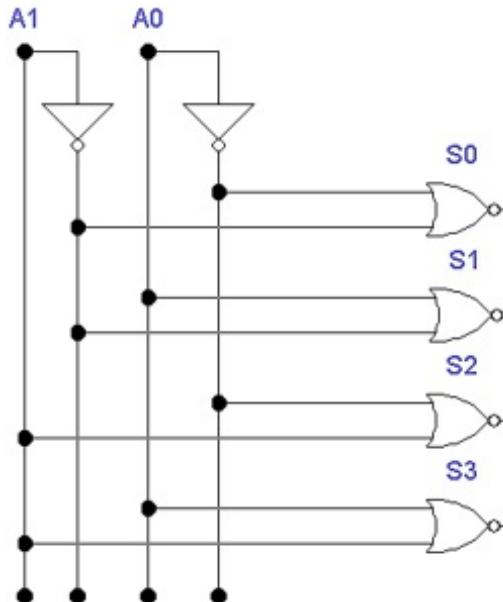

### 3.3.1 Le codeur (encodeur)